### NONRESIDENT TRAINING COURSE

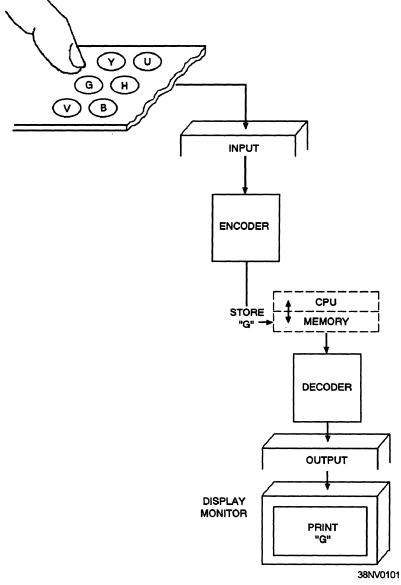

**April 1997**

# Fire Controlman

**Volume 3—Digital Data Systems**

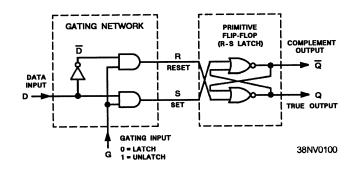

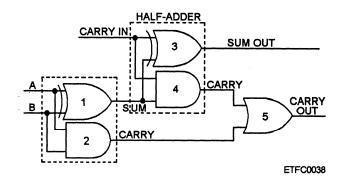

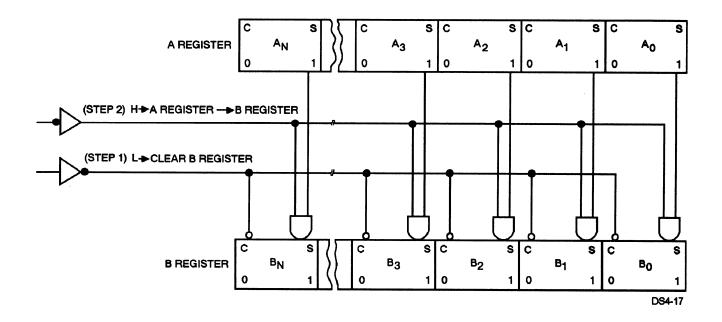

**NAVEDTRA 14100**

Although the words "he," "him," and "his" are used sparingly in this course to enhance communication, they are not intended to be gender driven or to affront or discriminate against anyone.

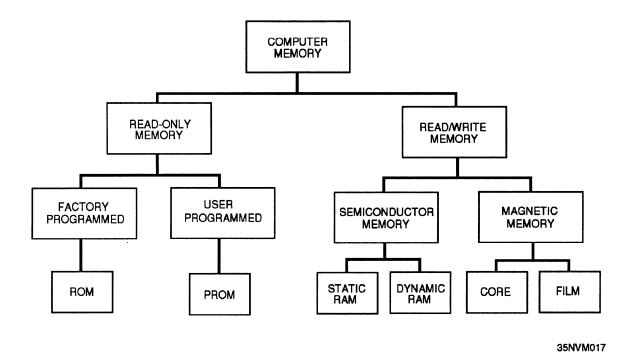

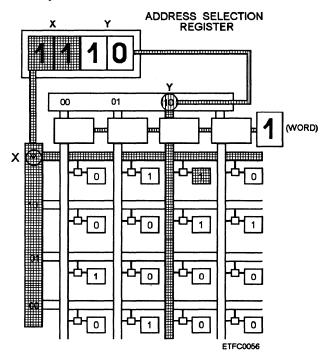

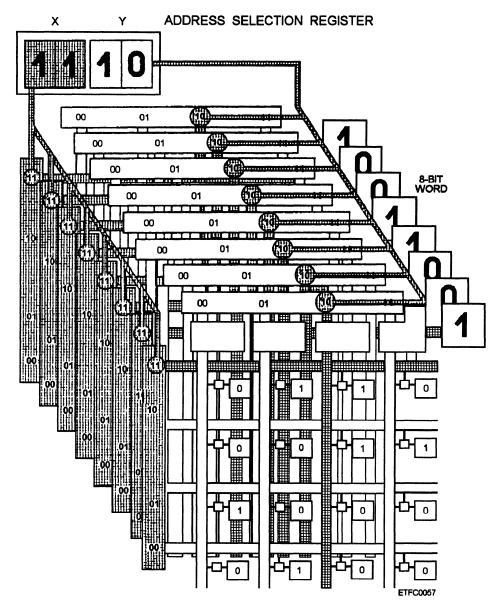

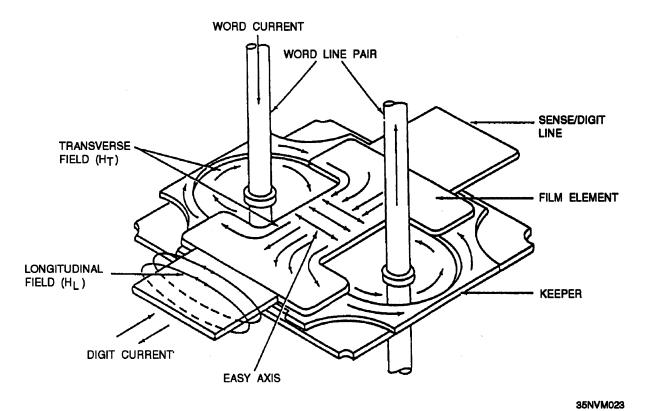

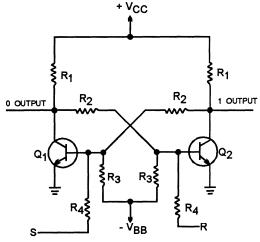

#### **PREFACE**

By enrolling in this self-study course, you have demonstrated a desire to improve yourself and the Navy. Remember, however, this self-study course is only one part of the total Navy training program. Practical experience, schools, selected reading, and your desire to succeed are also necessary to successfully round out a fully meaningful training program.

**COURSE OVERVIEW**: In completing this nonresident training course, you will demonstrate a knowledge of the subject matter by correctly answering questions on the following subjects regarding computers and their peripherals:

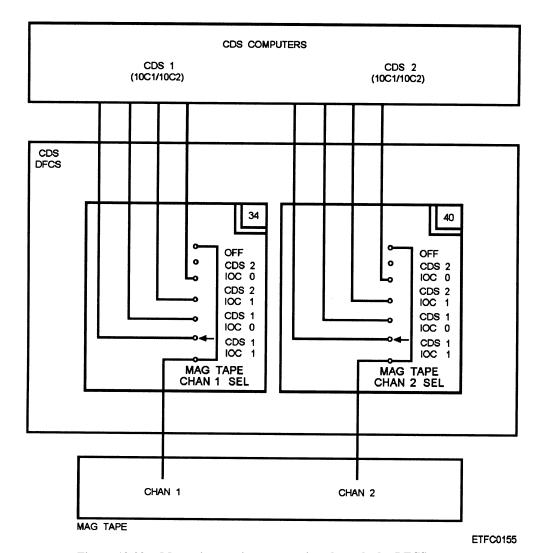

- fundamentals and operations,

- configurations and hardware,

- operator controls and controlling units,

- components and circuits,

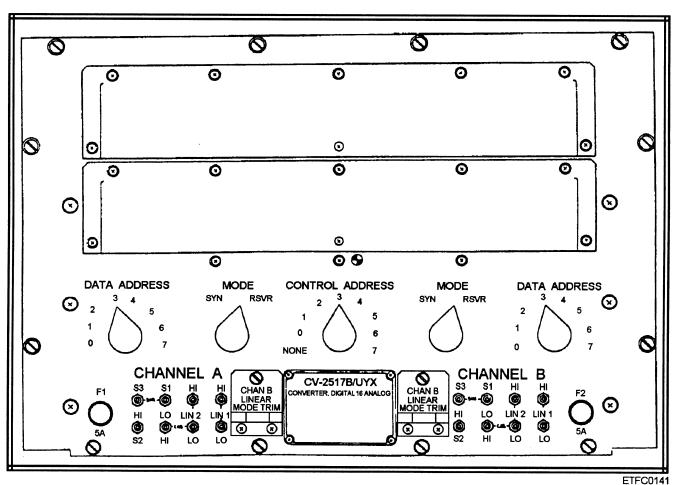

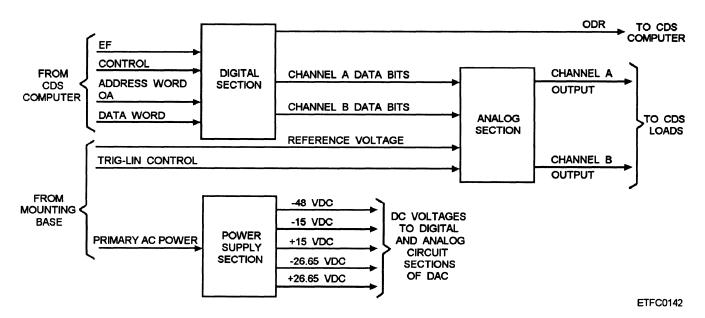

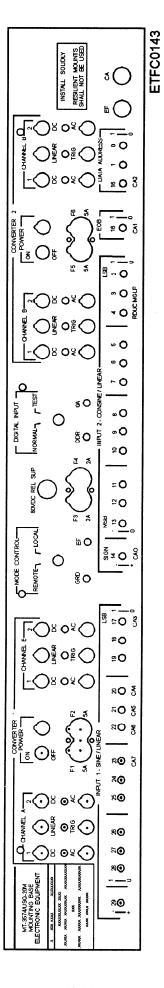

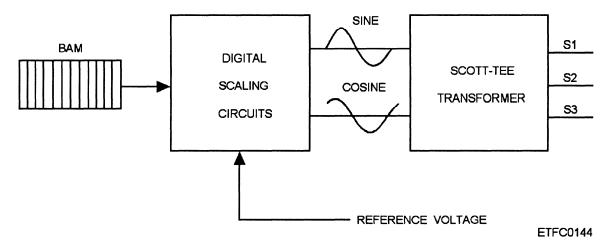

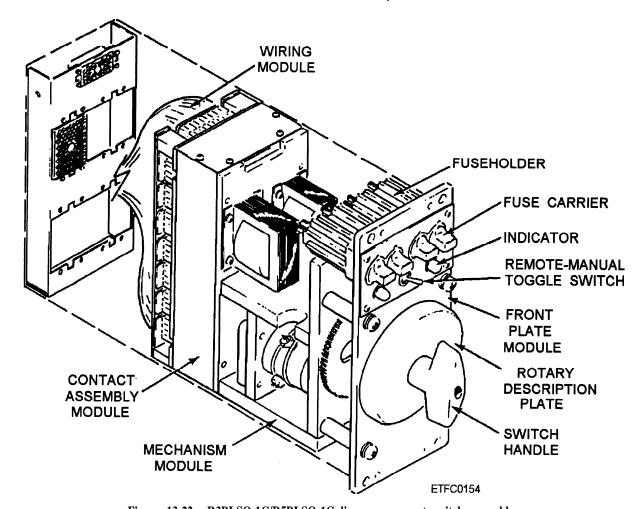

- central processing units and buses,

- memories,

- input/out and interfacing,

- instructions and man/machine interfaces,

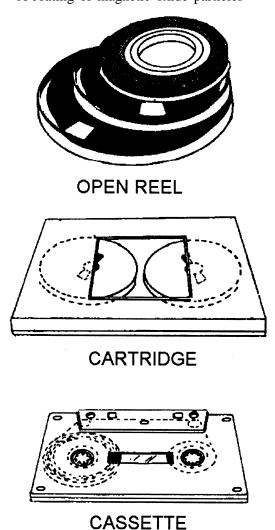

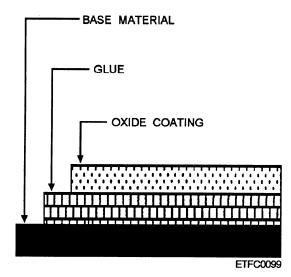

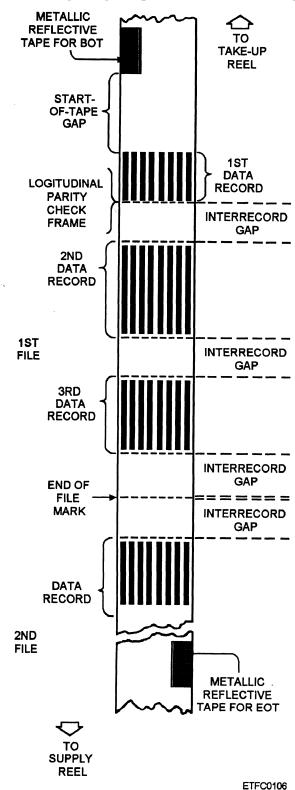

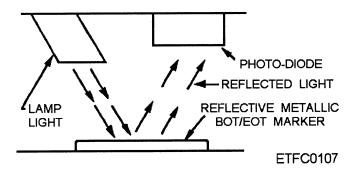

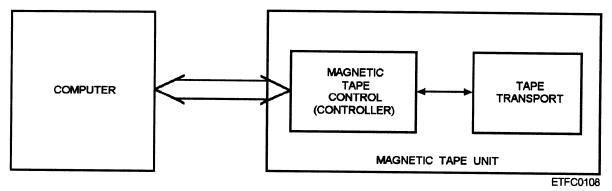

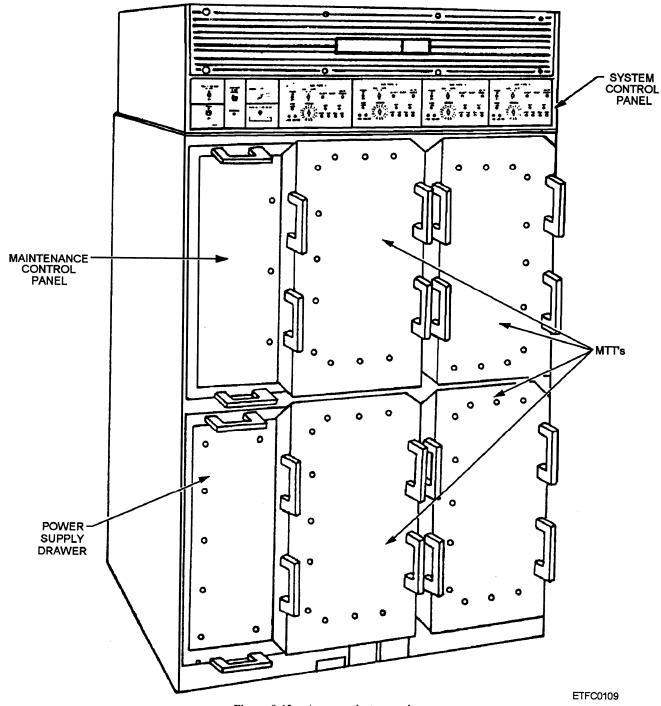

- magnetic tape storage,

- magnetic disk storage,

- CD-ROM storage,

- printers,

- data conversion devices, and

- switchboards.

**THE COURSE**: This self-study course is organized into subject matter areas, each containing learning objectives to help you determine what you should learn along with text and illustrations to help you understand the information. The subject matter reflects day-to-day requirements and experiences of personnel in the rating or skill area. It also reflects guidance provided by Enlisted Community Managers (ECMs) and other senior personnel, technical references, instructions, etc., and either the occupational or naval standards, which are listed in the *Manual of Navy Enlisted Manpower Personnel Classifications and Occupational Standards*, NAVPERS 18068.

**THE QUESTIONS**: The questions that appear in this course are designed to help you understand the material in the text.

**VALUE**: In completing this course, you will improve your military and professional knowledge. Importantly, it can also help you study for the Navy-wide advancement in rate examination. If you are studying and discover a reference in the text to another publication for further information, look it up.

1997 Edition Prepared by DSCS(SW/AW) Robert M. Maynard

Published by NAVAL EDUCATION AND TRAINING PROFESSIONAL DEVELOPMENT AND TECHNOLOGY CENTER

> NAVSUP Logistics Tracking Number 0504-LP-026-7670

### Sailor's Creed

"I am a United States Sailor.

I will support and defend the Constitution of the United States of America and I will obey the orders of those appointed over me.

I represent the fighting spirit of the Navy and those who have gone before me to defend freedom and democracy around the world.

I proudly serve my country's Navy combat team with honor, courage and commitment.

I am committed to excellence and the fair treatment of all."

### **TABLE OF CONTENTS**

| CHAPTER  | PAGE                                                 |

|----------|------------------------------------------------------|

| 1        | Fundamentals and Operations of Computers 1-1         |

| 2        | Computer Configurations and Hardware 2-1             |

| 3        | Computer Operator Controls and Controlling Units 3-1 |

| 4        | Computer Components and Circuits 4-1                 |

| 5        | Central Processing Units and Buses 5-1               |

| 6        | Computer Memories                                    |

| 7        | Input/Output and Interfacing                         |

| 8        | Computer Instructions and Man/Machine Interfaces 8-1 |

| 9        | Magnetic Tape Storage                                |

| 10       | Magnetic Disk Storage                                |

| 11       | CD-ROM Storage                                       |

| 12       | Printers                                             |

| 13       | Data Conversion Devices and Switchboards 13-1        |

| APPENDIX |                                                      |

| Ι        | Glossary of Terms and Acronyms                       |

| II       | References Used to Develop the TRAMAN AII-1          |

| INDEX .  |                                                      |

NONRESIDENT TRAINING COURSE follows the index

#### CREDITS

#### **Trademark Credits**

**Adobe** and **PostScript** are registered trademarks of Adobe Systems, Inc. in the U.S. and other countries.

**AMP** and **TERMI-POINT** are registered trademarks of AMP Incorporated.

Canon is a registered trademark of Canon U. S.A., Inc.

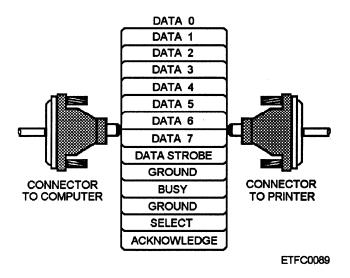

Centronics is a registered trademark of Centronics Corp.

**IBM** and **OS/2** are registered trademarks of International Business Machines Corporation.

Intel 80286 is a registered trademark of Intel Corporation.

LaserJet is a registered trademark of Hewlett-Packard Company.

Lin CMOS is a registered trademark of Texas Instruments Incorporated.

**Microsoft** and **MS-DOS** are registered trademarks of Microsoft Corporation.

UNIX and ST (straight Tip) are registered trademarks of AT&T.

#### INSTRUCTIONS FOR TAKING THE COURSE

#### **ASSIGNMENTS**

The text pages that you are to study are listed at the beginning of each assignment. Study these pages carefully before attempting to answer the questions. Pay close attention to tables and illustrations and read the learning objectives. The learning objectives state what you should be able to do after studying the material. Answering the questions correctly helps you accomplish the objectives.

#### SELECTING YOUR ANSWERS

Read each question carefully, then select the BEST answer. You may refer freely to the text. The answers must be the result of your own work and decisions. You are prohibited from referring to or copying the answers of others and from giving answers to anyone else taking the course.

#### SUBMITTING YOUR ASSIGNMENTS

To have your assignments graded, you must be enrolled in the course with the Nonresident Training Course Administration Branch at the Naval Education and Training Professional Development and Technology Center (NETPDTC). Following enrollment, there are two ways of having your assignments graded: (1) use the Internet to submit your assignments as you complete them, or (2) send all the assignments at one time by mail to NETPDTC.

**Grading on the Internet:** Advantages to Internet grading are:

- you may submit your answers as soon as you complete an assignment, and

- you get your results faster; usually by the next working day (approximately 24 hours).

In addition to receiving grade results for each assignment, you will receive course completion confirmation once you have completed all the assignments. To submit your assignment answers via the Internet, go to:

#### https://courses.cnet.navy.mil

**Grading by Mail:** When you submit answer sheets by mail, send all of your assignments at one time. Do NOT submit individual answer sheets for grading. Mail all of your assignments in an envelope, which you either provide yourself or obtain from your nearest Educational Services Officer (ESO). Submit answer sheets to:

COMMANDING OFFICER NETPDTC N331 6490 SAUFLEY FIELD ROAD PENSACOLA FL 32559-5000

**Answer Sheets:** All courses include one "scannable" answer sheet for each assignment. These answer sheets are preprinted with your SSN, name, assignment number, and course number. Explanations for completing the answer sheets are on the answer sheet.

**Do not use answer sheet reproductions:** Use only the original answer sheets that we provide—reproductions will not work with our scanning equipment and cannot be processed.

Follow the instructions for marking your answers on the answer sheet. Be sure that blocks 1, 2, and 3 are filled in correctly. This information is necessary for your course to be properly processed and for you to receive credit for your work.

#### **COMPLETION TIME**

Courses must be completed within 12 months from the date of enrollment. This includes time required to resubmit failed assignments.

#### PASS/FAIL ASSIGNMENT PROCEDURES

If your overall course score is 3.2 or higher, you will pass the course and will not be required to resubmit assignments. Once your assignments have been graded you will receive course completion confirmation.

If you receive less than a 3.2 on any assignment and your overall course score is below 3.2, you will be given the opportunity to resubmit failed assignments. You may resubmit failed assignments only once. Internet students will receive notification when they have failed an assignment—they may then resubmit failed assignments on the web site. Internet students may view and print results for failed assignments from the web site. Students who submit by mail will receive a failing result letter and a new answer sheet for resubmission of each failed assignment.

#### **COMPLETION CONFIRMATION**

After successfully completing this course, you will receive a letter of completion.

#### **ERRATA**

Errata are used to correct minor errors or delete obsolete information in a course. Errata may also be used to provide instructions to the student. If a course has an errata, it will be included as the first page(s) after the front cover. Errata for all courses can be accessed and viewed/downloaded at:

#### https://www.advancement.cnet.navy.mil

#### STUDENT FEEDBACK QUESTIONS

We value your suggestions, questions, and criticisms on our courses. If you would like to communicate with us regarding this course, we encourage you, if possible, to use e-mail. If you write or fax, please use a copy of the Student Comment form that follows this page.

#### For subject matter questions:

Address:

Address:

E-mail: n311.products@cnet.navy.mil

Phone: Comm: (850) 452-1503

DSN: 922-1503 FAX: (850) 452-1370 (Do not fax answer sheets.) COMMANDING OFFICER

NETPDTC N311

6490 SAUFLEY FIELD ROAD PENSACOLA FL 32509-5237

## For enrollment, shipping, grading, or completion letter questions

E-mail: fleetservices@cnet.navy.mil Phone: Toll Free: 877-264-8583

Comm: (850) 452-1511/1181/1859

DSN: 922-1511/1181/1859 FAX: (850) 452-1370 (Do not fax answer sheets.) COMMANDING OFFICER

NETPDTC N331

6490 SAUFLEY FIELD ROAD PENSACOLA FL 32559-5000

#### NAVAL RESERVE RETIREMENT CREDIT

If you are a member of the Naval Reserve, you may earn retirement points for successfully completing this course, if authorized under current directives governing retirement of Naval Reserve personnel. For Naval Reserve retirement, this course is divided into tow units, evaluated at 21 points.

Unit 1: 12 points upon satisfactory completion of assignments 1 through 8.

Unit 2: 9 points upon satisfactory completion of assignments 9 through 14.

(Refer to Administrative Procedures for Naval Reservists on Inactive Duty, BUPERSINST 1001.39, for more information about retirement points.)

### **Student Comments**

| <b>Course Title:</b> | Fire Controlman,     | ire Controlman, Volume 3—Digital Data Systems |              |     |  |  |

|----------------------|----------------------|-----------------------------------------------|--------------|-----|--|--|

| NAVEDTRA:            | 14100                |                                               | Date:        |     |  |  |

| We need some in      | formation about you: |                                               |              |     |  |  |

| Rate/Rank and Nam    | e:                   | SSN:                                          | Command/Unit |     |  |  |

| Street Address:      |                      | City:                                         | State/FPO:   | Zip |  |  |

| Your comments,       | suggestions, etc.:   |                                               |              |     |  |  |

**Privacy Act Statement:** Under authority of Title 5, USC 301, information regarding your military status is requested in processing your comments and in preparing a reply. This information will not be divulged without written authorization to anyone other than those within DOD for official use in determining performance.

NETPDTC 1550/41 (Rev 4-00

#### **CHAPTER 1**

# FUNDAMENTALS AND OPERATIONS OF COMPUTERS

#### **INTRODUCTION**

The computer is the heart and soul of any data system. It can be packaged in many sizes and configurations. It may be a general- or special-purpose type. It may handle analog or digital data, or both. It may be refereed to as a mainframe, minicomputer, or microcomputer. Regardless of what it is called or how it is configured, it will share certain common fundamental concepts and principles with all other computers. All computers gather, process, store, disseminate, and display data and information. Each computer is housed in a frame or cabinet. Each has a central processing unit (CPU), memory, input/output (I/O) section, and a power supply. How these are assembled in each computer will vary from unit to unit.

How much computing power a computer has is defined by the technology it uses and NOT by its physical size. A more powerd computer means greater speed, greater capacity and capability to store information, and a greater facility to accommodate additional peripheral (external) equipment. Our objective is to teach you the basic fundamentals and concepts of a computer, no matter what type you maintain.

- After completing this chapter, you should be able to:

- Describe the functions and purposes of a computer

- Differentiate between computer types based on their hardware characteristics

- Recognize the uses of computers and their functional operation

- Describe the types of computers used with tactical, tactical support, and non tactical programs

- Differentiate between full capability, reduced capability, and battle short mode in terms of computer operation and performance

- Compare the operational modes of computers including modes used in operation and maintenance

- Describe the security requirements associated with computers

Before you begin study of how a computer operates, let's take a look at the fundamentals and operations of computers in general. These include their functions, the different types of computers, and their functional operation. Also included are their operational uses, configurations/setups, and modes of operation.

#### TOPIC 1—COMPUTER FUNCTIONS AND TYPES

The computers the Navy uses vary from mainframes to microcomputers. Regardless of the types of computers and their operational uses, their functions are basically the same. Depending on the type of computer and the operational use, the methods will vary. First, we discuss the functions of computers, the different ways computers handle data, and the methods they use to accomplish this. Then we discuss the functional operation of computers.

#### COMPUTER FUNCTIONS

All computers must be able to gather, process, store, disseminate, and display data.

#### Gather Data

All computers, no matter what their size, must gather data before they can process the data. The operational program will dictate how the data is gathered—manually, automatically, or a combination of both.

Manually, an operator or technician will input the data to the computer. This can be done either directly or by a device external to the computer. The following are commonly used input devices:

- Keyboards

- Display consoles

- Data terminals

- Computer maintenance panels

- Storage devices (magnetic tape units, disk drive units, and paper tape units)

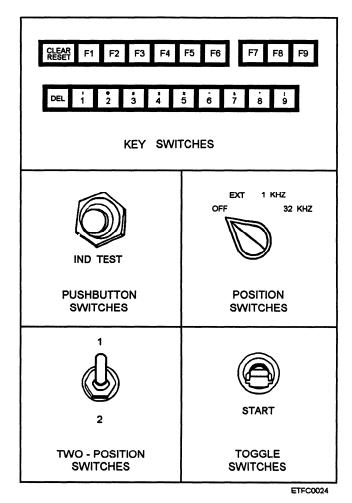

As an example, an operator at a console will input data via the console to the computer and the computer will process the data for storage, dissemination, or display depending on the functions of the operational program. Data may be input from a console using pushbuttons, switches, toggles, or a combination of these.

Automatically gathering data means the computer receives data from another system, subsystem, or equipment. The computer monitors for external requests through a series of programmed requests and acknowledges. The computer first sees the gathered data when it comes through the input section of the input/output section of the computer. Then depending on the operational program, the computer will either react immediately or store the data for future use. The following are examples of the sources from which computers gather the data automatically:

- Systems such as the fire control system

- Subsystems such as the combat direction system

- Data processing systems (another computer and conversion devices)

- Display systems via sensors (radar)

- Communication systems such as data links and local-area networks (LANs)

Many computer systems are designed to gather data using a combination of both the manual and automatic methods.

#### **Process Data**

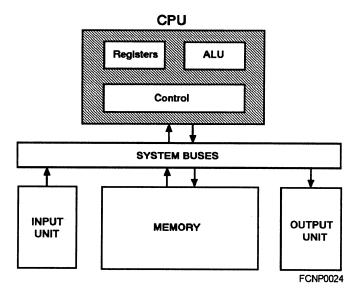

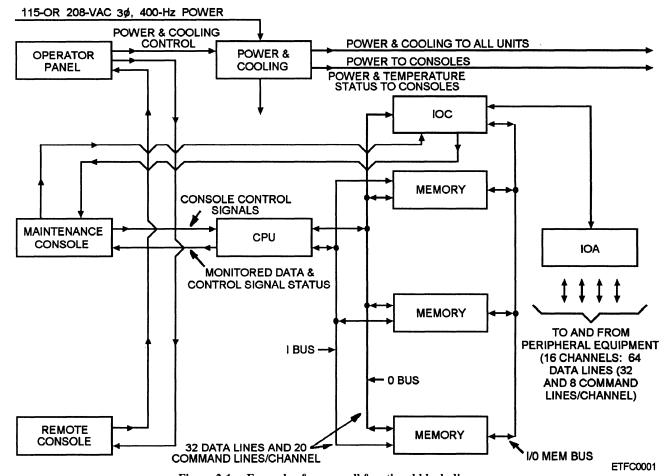

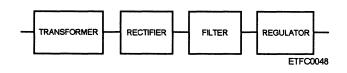

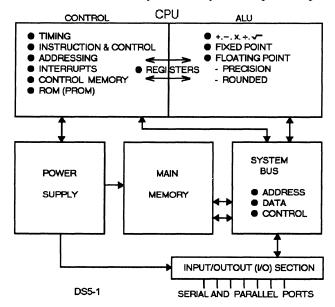

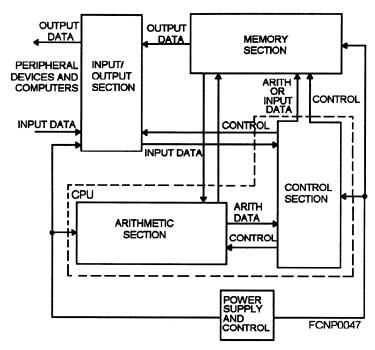

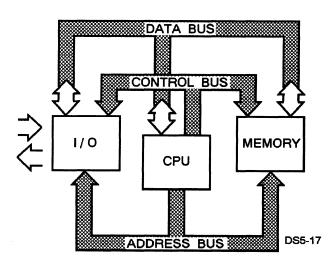

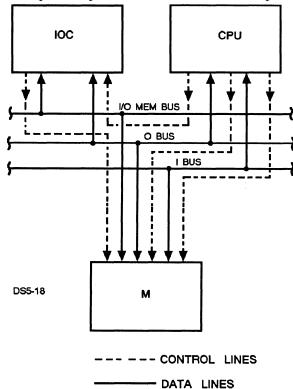

Processing data is the main function and the purpose of the computer. There are other systems, subsystems, and equipment that will work with the computer to help gather, store, disseminate, and display data; but processing the data is exclusively the computer's function. The heart of the computer—the place where the data is processed in a computer—is called the central processing unit (CPU). Figure 1-1 shows the basic configuration of a digital computer.

After the data is processed, it can be stored, disseminated, or displayed.

#### **Store Data**

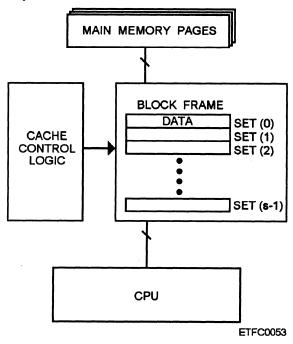

The computer can store data either internally or externally. Internally, the computer uses memory

Figure 1-1.—A basic functional composition of a digital computer.

banks. These memory banks can hold instructions and both processed and unprocessed data. Memory access time and memory capacity are the other main factors that determine how powerful a computer is.

Externally, computers can store data on magnetic disks (hard and floppy), magnetic tape, or paper tape. Disk drive units offer quicker access to the data than magnetic or paper tape units. On some systems, the disks can store more data than the internal memory of a computer. The amounts of each will depend on the design and requirements of the data system. Some systems internally store and process the data. Others depend heavily on the disks to hold and store the data, bringing the data into memory for processing, and then storing the results back onto disk.

#### **Disseminate Data**

After the computer has processed the data, it can send it to the I/O section or an I/O unit for immediate or future dissemination to various equipments. The data will exit the output section of the computer's input/output section. It can be sent to an output device such as a printer, or to one of many storage devices such as a magnetic tape or disk unit. It can also be sent to a subsystem, such as a display system, via its associated equipment.

#### **Display Data**

Computer systems display two general types of data—data related to the mission of the system and status information related to operation of the system and hardware performance. The computer relies on peripheral equipment, such as printers and display units, to display the processed data—the mission related output of the operational program. Your interest in output generally relates to whether the data is sent properly by the computer and is displaying properly. In other words, you want to know the computer system is functioning properly. The content of the data is usually a secondary interest to you and a primary interest to the user/operator.

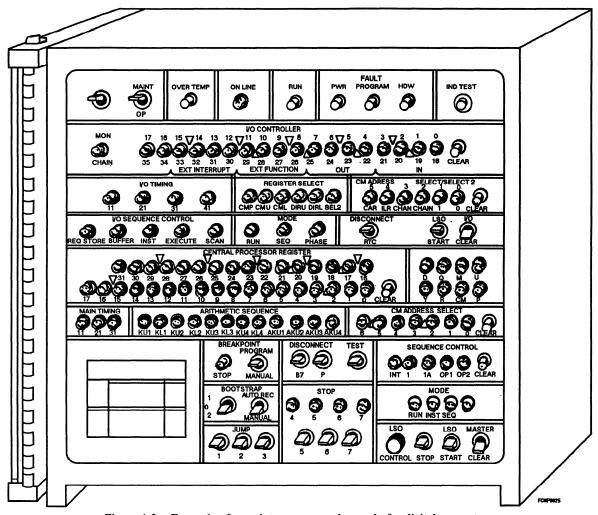

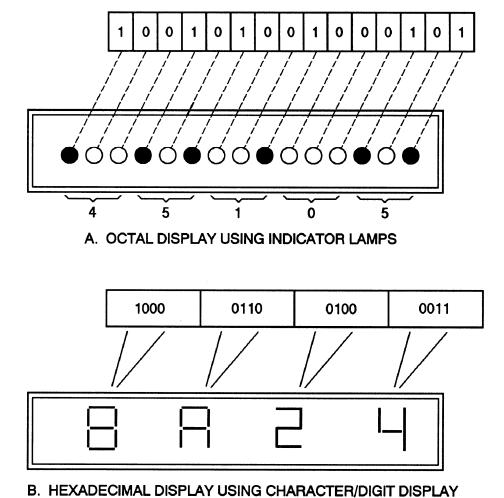

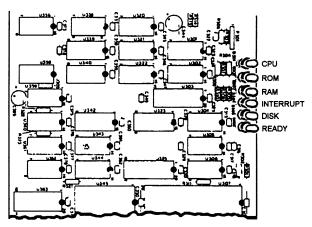

The other type of data/information that can be displayed relates to the operation of the system. This includes operator information, system error messages, and indications of system problems. You will be particularly interested in this information. The maintenance panels and data terminals can display real-time data and provide you with current status of the operational program. For example, the maintenance panels of some computers have registers where the presence or absence of indicator lamps can indicate to the technician if the computer is communicating with a

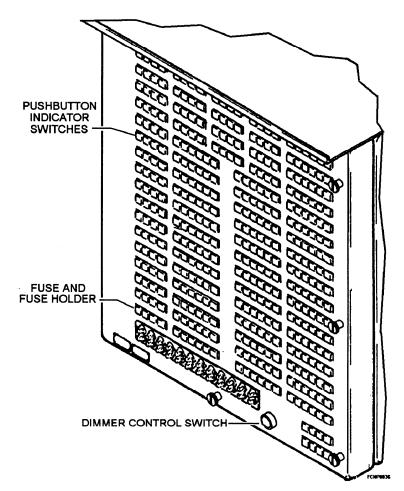

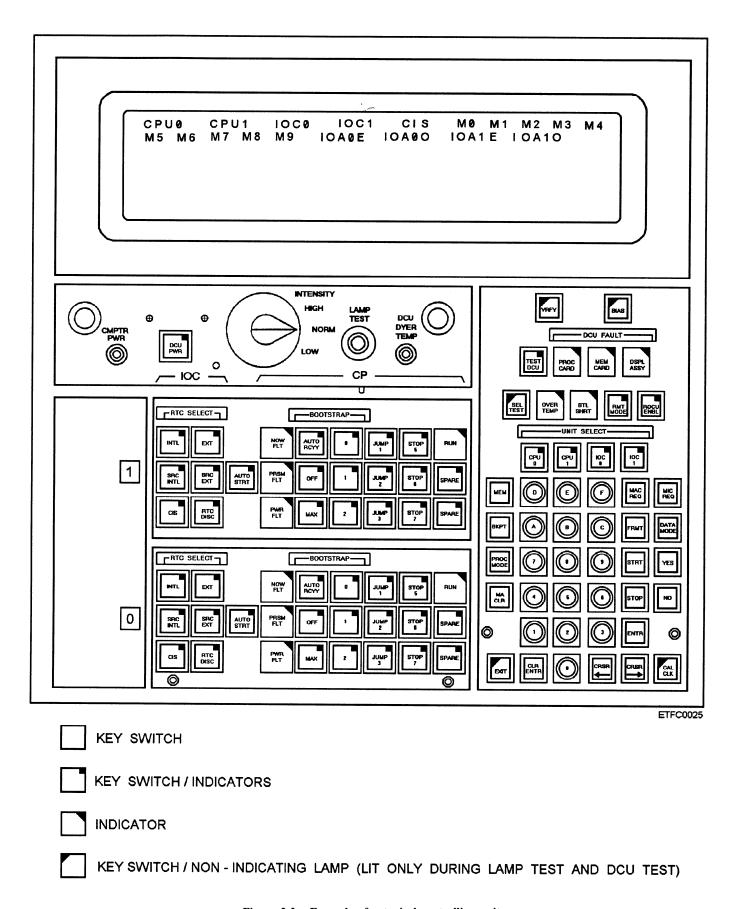

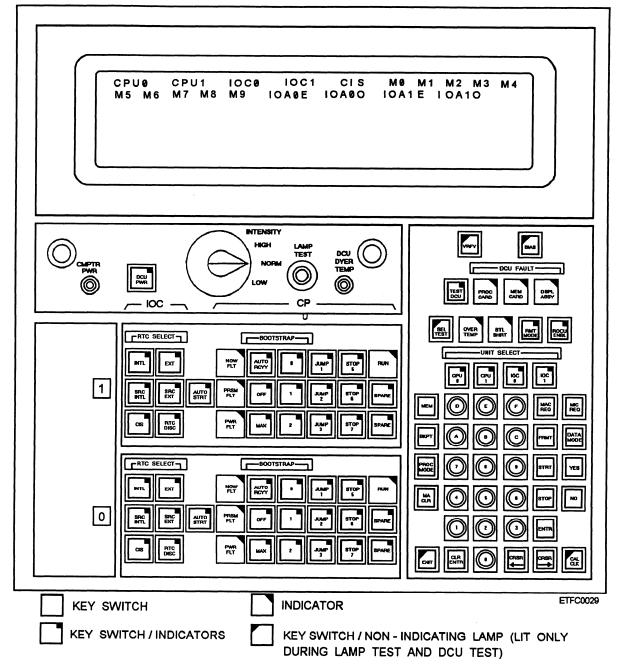

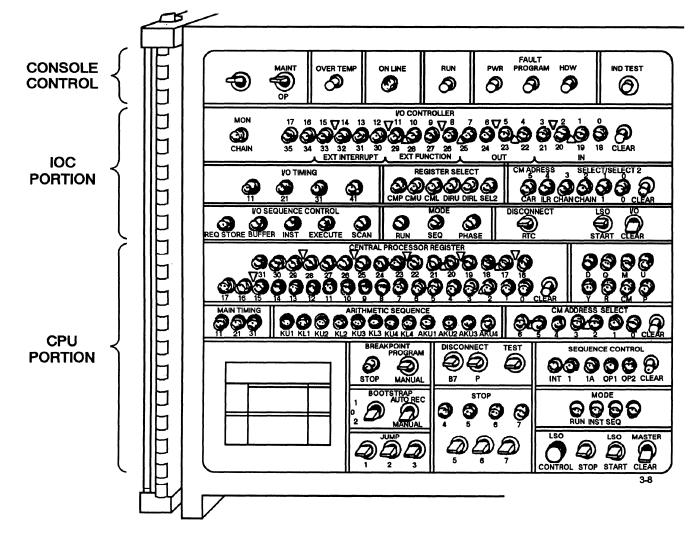

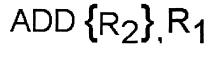

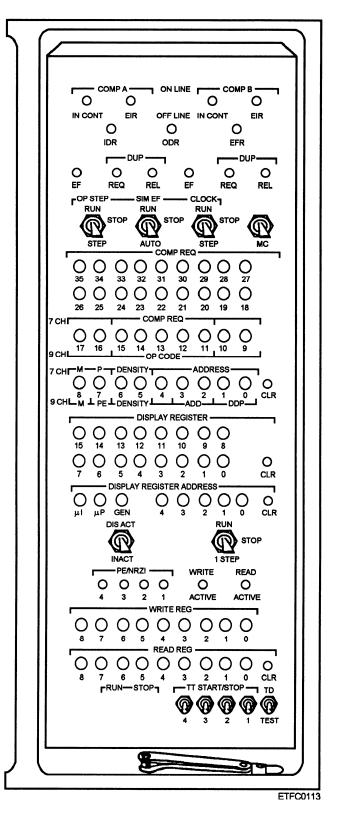

subsystem such as a display or communication subsystem. This is a very useful tool when you are performing maintenance, both preventive and corrective. Figure 1-2 is an example of a maintenance console panel. Notice the indicator lights for the I/O controller, I/O timing, Mode, Central Processor Register, and soon. These will provide you with status information. For example, you can monitor the I/O controller register to see if the computer is interfacing with a particular subsystem such as display or communications. Look to see if the indicator of that channel is illuminated (either flashing or constantly lit). Or, you could look at the contents of a particular register in the CPU by selecting that register while installing a patch to a program using an inspect and change procedure or utility.

#### TYPES OF COMPUTERS

In general terms, computers can be classified into three categories: mainframe computers minicomputers, and microcomputers. A computer's power is determined by the technology it uses, NOT its physical size. Greater speed, greater capability and capacity to store information, and greater facility to accommodate additional peripheral (external) equipment will make one computer more powerful than another regardless of their overall physical sizes. We do not go into detail on each of the different types of computers. Rather, we identify examples of each and point out their physical and internal differences. This will prove valuable when you are maintaining them. Let's take a look at the types of computers you will maintain in the Navy. Later in this manual, you will study the internal workings of computers-their basic functional operation.

#### **Mainframe Computers**

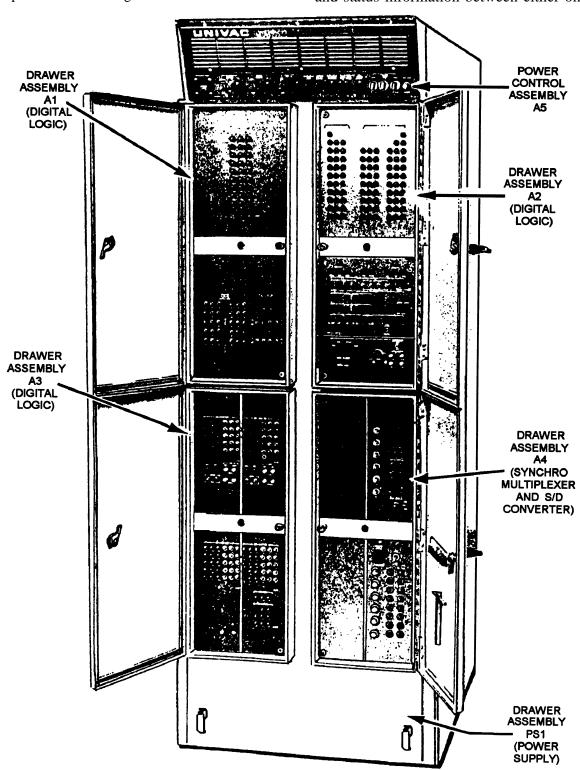

Mainframe computers are physically the largest computers you will maintain. Their ruggedness makes them better suited than microcomputers and minicomputers to handle the mechanical shock and vibration, salt spray, temperature and humidity found aboard Navy vessels. The mainframes you will maintain are general-purpose, digital data computers with multiprocessing capability.

Mainframe computers are considered the heart of the afloat and ashore tactical and tactical support data systems. These mainframe computers are big, fast, multiprocessor computers with correspondingly large memories and multiple I/O channel capabilities. They process large volumes of data and require a lot of program flexibility. Their operational programs are

Figure 1-2.—Example of a maintenance console panel of a digital computer.

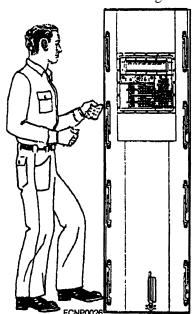

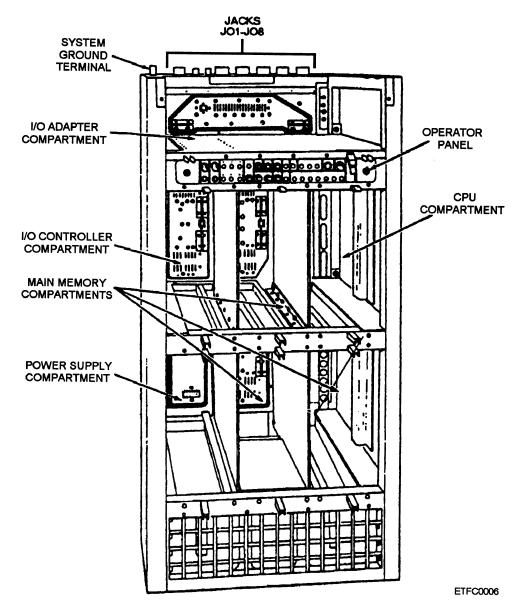

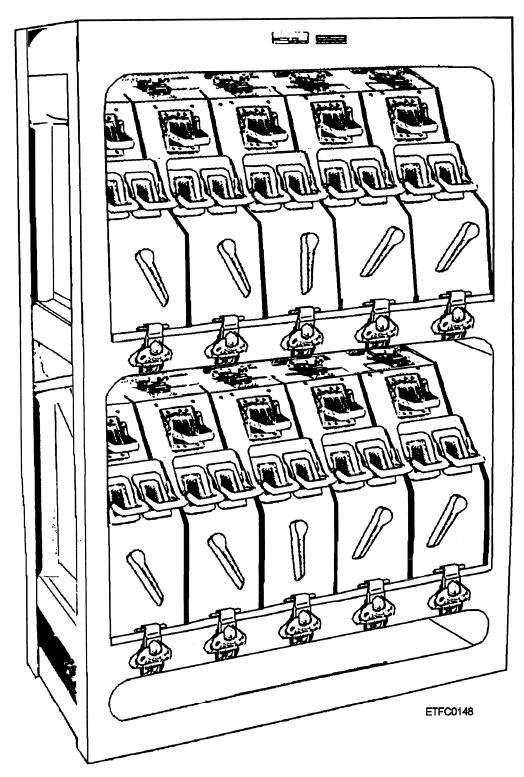

complex, and as systems are updated, the programs must be revised to meet the new demands of the fleet. Operational programs for mainframe computers are supported by technical teams external to the command. Two examples of mainframes are the AN/UYK-7(V) and the AN/UYK-43(V) computers. They are general-purpose, militarized, digital data computers with large-scale memories, I/O capabilities, and multiprocessing capabilities that allow a number of CPUs to operate simultaneously in the same system. They interface with other mainframes and peripherals in the data processing subsystem, the display subsystem, and the communication subsystem. Training is obtained through formal C schools and is NEC producing. Figure 1-3 is an example of one of the Navy's mainframe computers.

Some physical features of mainframe computers are highlighted as follows:

• <u>Large rugged frame</u> or cabinet —Contains individual modules or units; central processor unit (CPU), memory modules, input/output controller

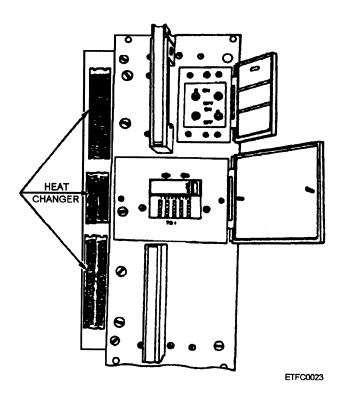

and/or adapter unit with I/O connectors, heat exchangers for each module or unit, power supply unit(s), and blower motors for cooling.

Figure 1-3.—Example of a mainframe computer.

- Operator console —Controls operation of the computer at the computer. This console/panel is usually located above the logic chassis but separate from the maintenance console/panel. It contains the controls and indicators necessary to initiate computer operations. You can turn on power to the system and load the operational program and start its execution.

- <u>Remote console</u> —Controls operation of the computer from a remote location. Performs the same functions as an operator console except it does not apply power to computer set.

- <u>Maintenance console panel/display control unit</u> (<u>DCU</u>) —Controls operation of the computer and is used to perform maintenance (preventive and corrective).

- <u>Specific power requirements</u> (frequency and voltage).

- <u>Specific cooling requirements</u> (air and/or liquid cooling).

#### Minicomputers

Minicomputers are mid-range computers. They are smaller in physical size than the large mainframes used for tactical and tactical support operations. 'hey are also built for ruggedness. Minicomputers are capable of stand-alone or self-contained operation, or of being an embedded processor in a system or other type of digital device. Minicomputers are generally used in applications that don't require the faster computational speeds or larger memory capacities available on mainframes. These computers also have program flexibility. Minicomputers receive external technical support for the operational programs they use. The programs for minicomputers are updated as specific jobs or applications are updated and revised.

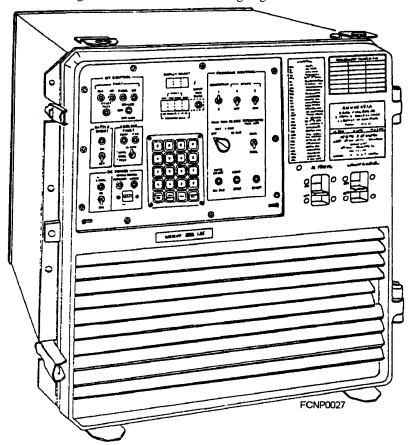

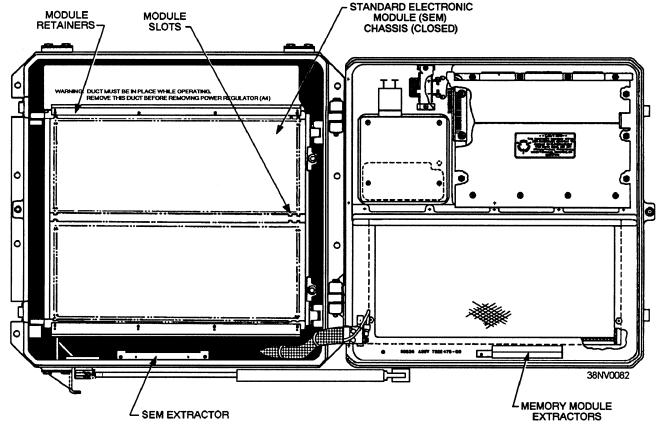

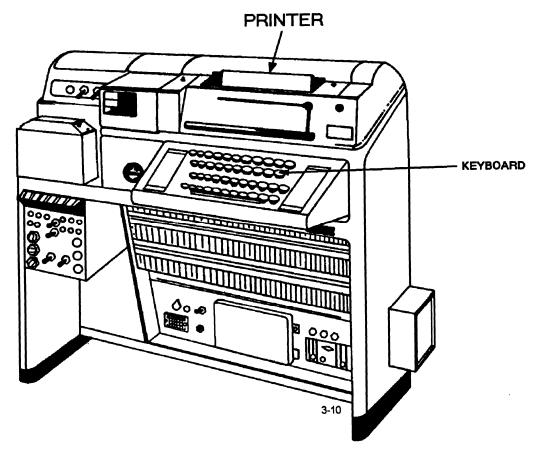

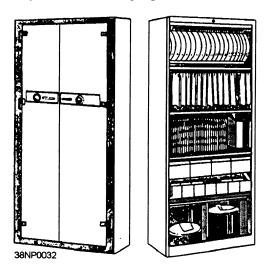

Some examples of minicomputers are the minis used as interface computers with communications or radar systems. Minis are also used as the host computers for the Shipboard Nontactical ADP Program (SNAP I, SNAP II, and SNAP III) Systems. Training for minicomputers is provided through formal A, C, and FTC schools and may be NEC producing. SNAP system training is an example of an NEC-producing school. Figure 1-4 is an illustration of a typical minicomputer.

Some physical features of minicomputers are highlighted as follows:

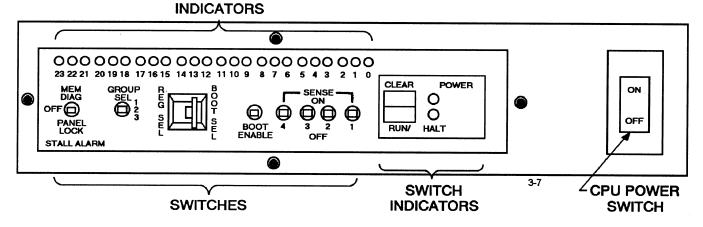

Figure 1-4.—Example of a minicomputer.

- Large to medium rugged frame or cabinet— Some frames or cabinets use a stationary or sliding chassis or assemblies or stationary racks or card cages that contain individual modules or printed circuit boards. The functional and support areas include a central processor unit (CPU), memory units, input/output controller boards for various peripherals, I/O connectors, power supply unit(s), and blower motors for cooling. (NOTE: Some minicomputer frames or cabinets also contain the peripheral—disk drive units, magnetic tape units, and paper tape units.)

- Control and Maintenance Panel (CMP) or computer control panel —Controls operation of the computer and is used to perform maintenance (preventive and corrective).

- <u>Specific power requirements</u> (frequency and voltage).

- <u>Specific cooling requirements</u> (air and/or liquid cooling).

#### **Microcomputers**

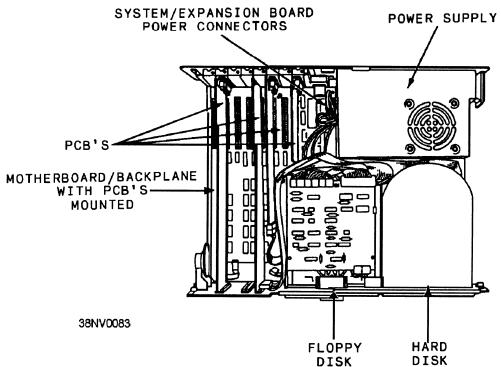

Microcomputers, personal computers (PCs), are small, lightweight, and portable. Some of them are more powerful than some of the older, larger mainframes and minicomputers. Microcomputers are unique in that the heart of the computer (the CPU) is contained on a single integrated chip (IC) and the entire computer system is contained on a handful of printed circuit boards located inside a small compact frame or cabinet. In some cases a complete microcomputer is located on a single chip; the CPU, co-processor, and memory. Some micros/PCs are high-speed, multi-user, multi-tasking units. Traditionally micros are used for word processing, database management, spreadsheets, graphics, desktop publishing, and other general office applications. Currently, micros and PCs are being used for tactical support systems, such as Naval Intelligence Processing Systems (NIPS) and Joint Operational Tactical System (JOTS). Micros and PCs can also be used as a SNAP system for shorebased operational commands, such as ASWOC. The operational programs for PCs used for a tactical support system are supported externally by technical teams. These operational programs are also updated as systems are added or replaced. Programs that are used for word processing, graphics, and soon are abundant and can be obtained through civilian vendors and software support teams such as Commander Naval Computer and Telecommunications Command (COMNAVCOMTELCOM). Training for microcomputers is obtained through formal A schools,

civilian contractor schools, and OJT. Training for micros is not NEC producing. Figure 1-5 is an illustration of a typical microcomputer.

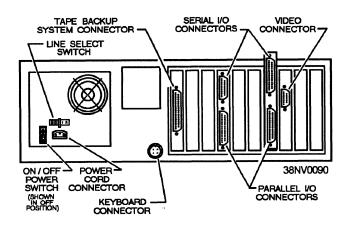

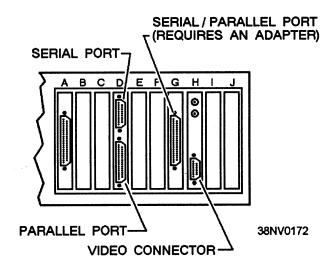

The physical features of microcomputers are very different from mainframes and minis. The following is a brief description of a typical PC/desktop system.

- <u>Small compact frame or cabinet</u> —PCs are unique in that the frame or cabinet contains the majority of the components for a complete system. A typical PC frame or cabinet contains the following components:

- Backplane or motherboard for printed circuit boards

- A central processor unit (CPU) and memory printed circuit board(s) (pcb) (NOTE: In some cases the CPU and memory are located on the same pcb.)

- Input/output pcb

- Disk controller pcb

- Video controller pcb

- Data storage devices: Hard disk drive units, floppy disk drive units, and/or tape cassette units

- I/O connector: Parallel or serial communications

- A small fan: No special cooling requirements; the unit relies on ambient temperature of the room or space

- Power supply: No special requirements

- <u>Display monitor</u> —Display monitors are output devices for visual displays of data, and may have monochrome or color displays.

Figure 1-5.—Example of a microcomputer.

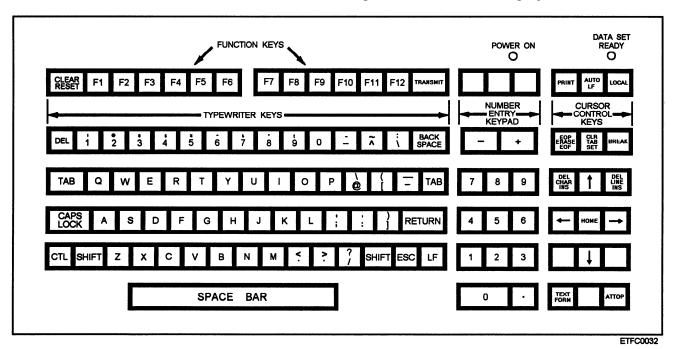

- <u>Keyboard</u> Keyboards are input devices used to control operation of a computer.

- <u>Printer</u> Printers are output devices for producing printed material.

- <u>Modem</u> —Modems are optional components used to communicate with mainframes, minicomputers, and microcomputers through existing phone lines.

- Mouse —Another optional component is a mouse. A mouse is an input device used to highlight text, move the cursor, and select commands and functions without using the keyboard. A mouse can be used in combination with a keyboard to control computer operations.

### TOPIC 2—FUNCTIONAL OPERATION OF COMPUTERS

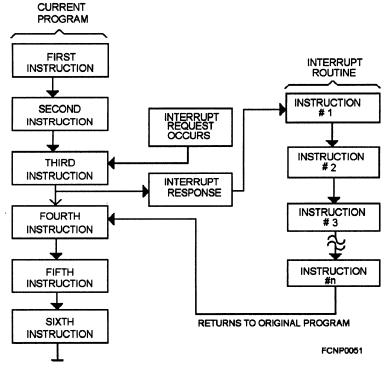

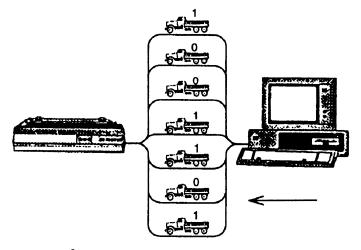

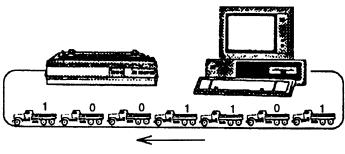

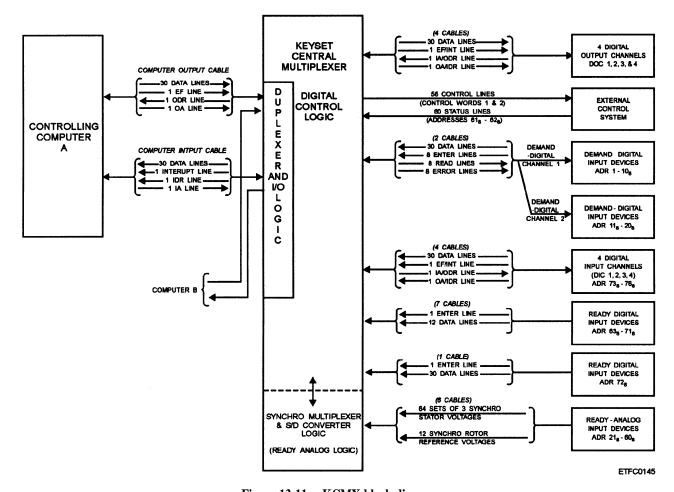

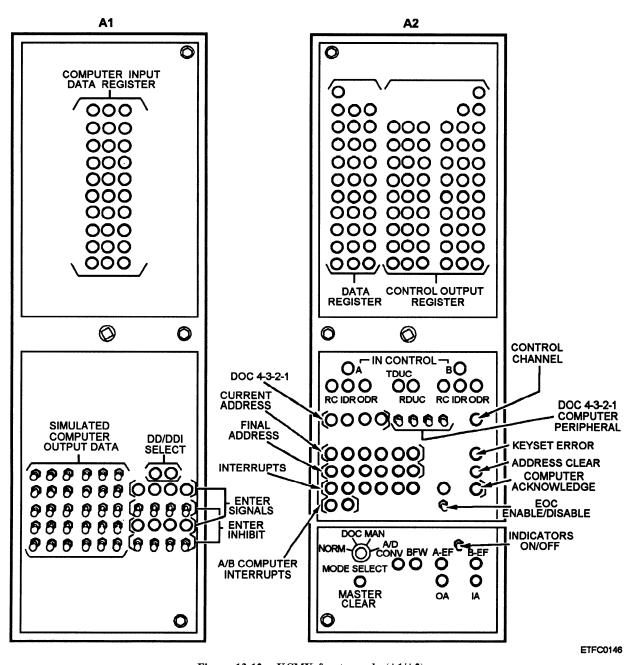

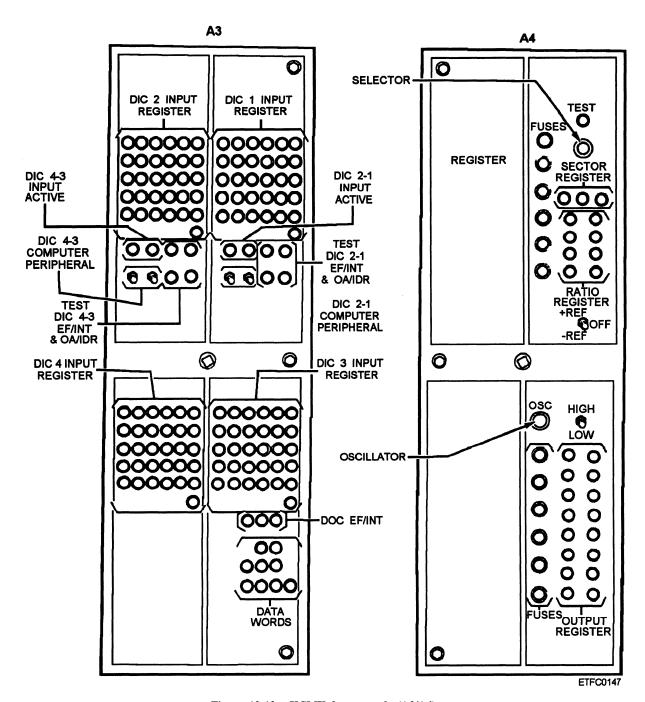

At the heart of every data system is a computer. All digital data made available on any system has been processed by the computer. The computer oversees the operation of any data system. Through a coordinated series of interrupts, requests, and acknowledges, the computer exchanges data with other computers, peripherals, and the subsystems required for that system.

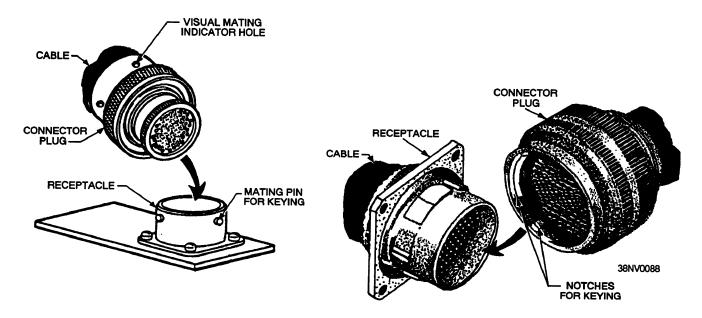

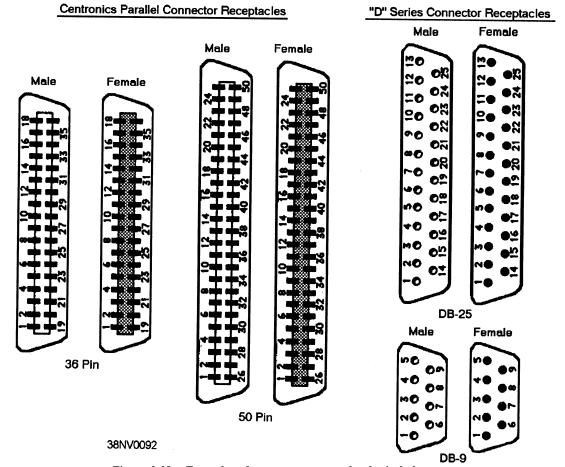

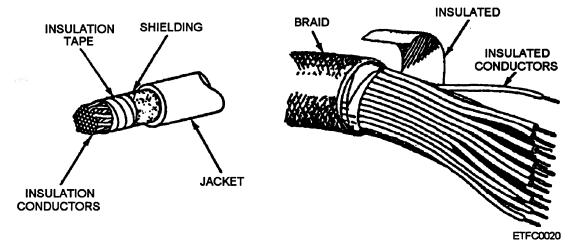

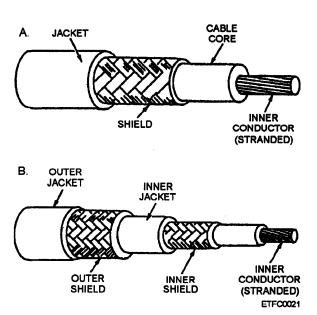

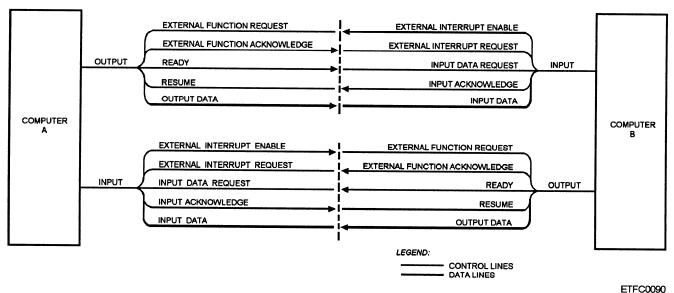

The signal flow between systems, subsystems, and equipment is all coordinated by the operational program of the computer(s). Exchange of signals between the systems, subsystems, and equipment is accomplished through a coordinated series of priorities where interrupts, requests, and acknowledges determine when the data will be exchanged. The type of data exchanged includes status signals, control signals, and data words. Interfacing between the computer(s) and other systems, subsystems, and equipment requires some type of cabling—standard shielded and unshielded cables, fiber-optic cables, and ribbon cables, and their associated connectors. Methods of interfacing include parallel and serial data transfers.

#### OPERATIONAL USES OF COMPUTERS

You may have the opportunity of maintaining three basic types of data systems: tactical, tactical support, and nontactical. all three rely on one or more computers to make rapid calculations and make information available.

#### **Tactical Systems**

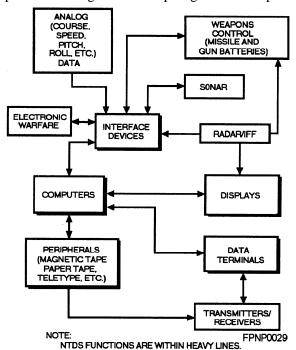

A computer is the heart of the Combat Direction System (CDS)/Naval Tactical Data System (NTDS), which is a subsystem of the ship's combat system. CDS/NTDS receives data from ship's sensors and other ships using tactical data links. The CDS/NTDS consists of high-speed digital computers, peripherals, displays, communication links, and computer programs. The CDS/NTDS hardware is divided into three major equipment groups (subsystems) as follows:

- Data Processing Group

- Data Display Group

- Data Communications Group

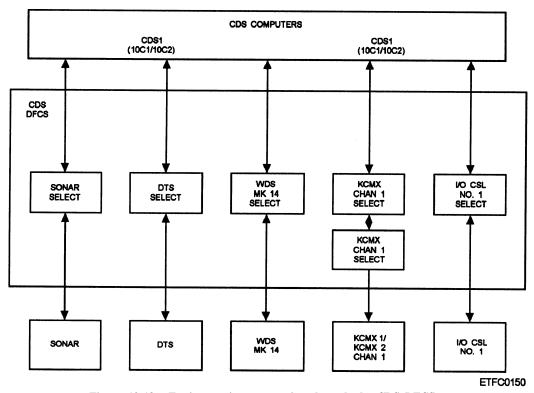

The data these subsystems generate and feed back to the data processing subsystem is stored, processed, and distributed by the operational program. The computer is part of the data processing group and coordinates the operations within CDS/NTDS and makes the information available to other major subsystems within combat systems: radar/IFF, weapons (guns, missiles, and underwater), electronic warfare, and navigation. The CDS/NTDS is a real-time system. The type of computer used in a tactical data system is a mainframe such as the AN/UYK-7(V) or AN/UYK43(V) computer. The number of computers used in a tactical data system depends on the class of ship and its configuration/setup. Figure 1-6 is a portion

Figure 1-6.—Simplified block diagram of a tactical data system (CDS/NTDS).

of a simplified block diagram of a typical CDS/NTDS in a tactical data system.

Another example of a tactical data system is the Integrated Tactical Amphibious Warfare Data System (ITAWDS).

#### **Tactical Support Systems**

Tactical support platforms include a variety of systems. Unlike tactical data systems, tactical support systems generally use either mainframes or micros as their operational computers. Depending on the system, tactical support systems can use a single computer or a multiple computer configuration. The computers in tactical support systems also interface with other computers, peripherals, displays, communication links, and operational programs. Let's look at three examples: ASW systems, JMCIS, and NIPS.

ASW SYSTEMS. —ASW systems deal primarily with antisubmarine warfare. They provide active and passive search, detection, tracking, and classification operations necessary to engage and destroy subsurface or surface targets. They support ASW airborne systems. ASW systems include the Antisubmarine Warfare Operations Center (ASWOC) and Carrier-Antisubmarine Warfare Module (CV-ASWM) systems. These systems use a single computer as their central point of operation.

The computers in these systems interface with the following subsystems or equipment within their subsystem:

- <u>Command and Control Subsystem</u> —Controls the data to and from this subsystem and other subsystems through the ADP Subsystem and Display Subsystem.

- <u>Communication Subsystem</u> —Allows communication between Maritime Patrol Aircraft (MPA) or Surface Units and/or ASWOCs, CV-ASWMs, and FHLTs. Communication is via secure voice or secure data networks.

- Fast Time Analysis System (FTAS) Subsystem (ASWOCs and CV-ASWMs only) —Analyzes acoustic and nonacoustic data provided by mission aircraft.

JOINT MARITIME COMMAND INFORMATION SYSTEMS. —The Joint Maritime Command Information Systems (JMCIS) is an informational data system used to provide data to designated flagships. It

is used to effectively conduct battle-management of the tactical situation. The JMCIS consists of a data processing subsystem and a video processing subsystem. The data processing subsystem includes desktop computers (DTWTAC-n¹) with single and dual monitors, printer plotters, and printers. The video processing subsystem includes high and low resolution monitors, large screen displays, and video switch. Communication between DTC/TAC-n in the data processing subsystem and video processing subsystem is accomplished via a Genser fiber-optic LAN. JMCIS gathers data from a variety of external links including OTCIXS, Flag communication, Fleet Broadcast, and Link 11 or Link 14.

NAVAL INTELLIGENCE PROCESSING **SYSTEM.**—Naval Intelligence Processing System (NIPS) integrates up-to-the-minute tactical intelligence with national and fleet-produced database intelligence information. Data is gathered from the Naval Modular Automated Communication System (NAVMACS), Ocean Surveillance Product (OSP), Generic Front End Co-Processor (GFCP), Automatic Tracking Point (ATP), Fleet Imagery Support Terminal (FIST), video diskplayers, and optical disk recorders, and, in turn, is disseminated to GFCP, ATP, and Tactical Aviation Mission Planning System (TAMPS). The NIPS uses the DTC/TAC-n in a LAN configuration as its operational computers. The other hardware interfaces include hard drives, color printers, plotters, tape backup units, a camcorder, and light table. The NIPS uses both MS-DOS and the UNIX operating system to process and manage its mapping/imagery workstation and message handler workstation. Depending on the vessel, the NIPS can be a basic system, as on a multipurpose amphibious assault ship (LHD), or it can be a much larger system with multiple workstations and remotes, as on a carrier (CV).

#### **Naval Tactical Command Support Systems**

Naval Tactical Command Support Systems include those systems that handle data used for administrative purposes and office functions. They support organizational and intermediate-level maintenance, supply and financial management, and administrative applications. The types of computers generally used are minicomputers and microcomputers. Nontactical systems include the Shipboard Nontactical ADP Program (SNAP I, SNAP II, and SNAP III) Systems and PC.

1

$<sup>^{1}</sup>$ n = configuration number.

**SNAP SYSTEMS.**—The SNAP systems are used primarily to reduce the administrative workload associated with equipment maintenance, supply and financial management, and personnel administration.

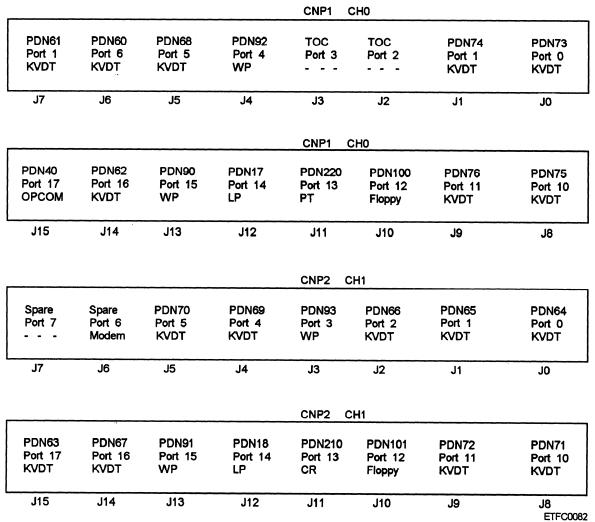

Because the SNAP systems differ in their subsystem configurations, we are only listing the equipment with which they are both capable of interfacing. Some SNAP systems communicate via modems and specialized interfacing techniques and hardware. SNAP computers interface with the following equipment:

- Disk drive units

- Magnetic tape drive units

- Keyboard/video display units (KVDTs

- Printers—High speed, display, line, and word processing

Some SNAP systems use specialized communications hardware and interfacing methods. They use processors, adapters, and modems.

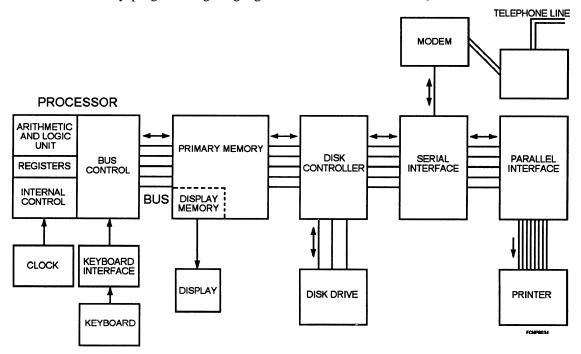

**PERSONAL COMPUTER/DESKTOP MICROCOMPUTER SYSTEMS.**—Personal computer/desktop microcomputer systems (PC) software enables PC systems to perform word processing, database management, spreadsheets, graphics, and desktop publishing. For these functions, off-theshelf software packages can be installed in each PC system. There are also many programming languages

for programming the PC; they include BASIC, FORTRAN, COBOL, PASCAL, C, and many others. These languages allow you to design your own programs to perform functions exactly the way you want them. Figure 1-7 is a simplified block diagram of a PC system.

A PC can interface with other hardware. The following are examples:

- Secondary storage units—hard disk drive units, floppy disk drive units, and/or tape cassette units

- Monitor—color or monochrome

- Printer

- Modem

PCs can be operated as stand-alone systems or as remote units to a larger system. They can also be configured in local-area networks (LANs). With LANs, the PC can talk with other PCS and share data files, peripherals, and software.

#### COMPUTER SYSTEMS CONFIGURATIONS AND SETUPS

The computer system you are working with must be correctly configured/set up or it will be useless for operational purposes. You will need to be able to configure and set up the computer system for both operational purposes and for maintenance. You need to be aware of two things—the hardware and the software.

Figure 1-7.—A simplified block diagram of a PC system.

The type and number of computers that make up a system have a direct bearing on the configuration and setup of a system. Some systems require two or three computers connected in tandem. An example is a CDS/NTDS for a particular class of ship, which may use a three-bay/one-bay configuration for its CDS/NTDS. Others have only one computer. An example is a PC in an office setting.

#### Hardware

When configuring or setting up a computer system for operation or maintenance, check your computer's technical, system operations, or combat systems technical operations manuals for the correct physical setup. Set up includes the following:

- Physical design

- Operator controls

- External controls

**PHYSICAL DESIGN.** —The design of the computer system will predetermine how and where module units and printed circuit boards need to be inserted and where cables are to be connected. Once these items are correctly installed and connected, the next step is to ensure that all operator controls are in their correct positions.

**OPERATOR CONTROLS.** —Computers can be controlled directly at the computer and in some cases remotely through panels/consoles. Mainframe and large minicomputers usually have controls for the computer at your fingertips. You can control the computer from several panels/consoles as follows:

- Maintenance panel/console

- Operator panel/console

- Remote panel/console (usually only mainframes for tactical systems have this capability)

The types of controls these units most often use are discussed in more detail in chapter 3 of this manual. You can also control the computer's mode of operation directly from the computer's maintenance panel/console or operator's panel/console. This feature is not available on all computers.

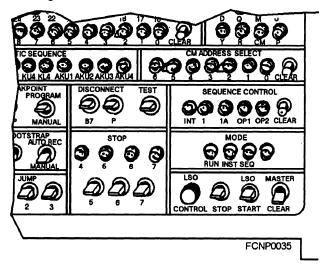

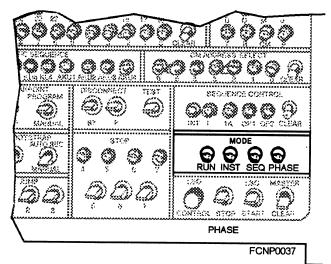

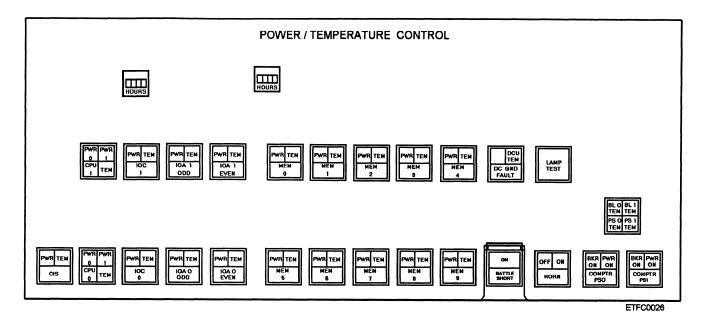

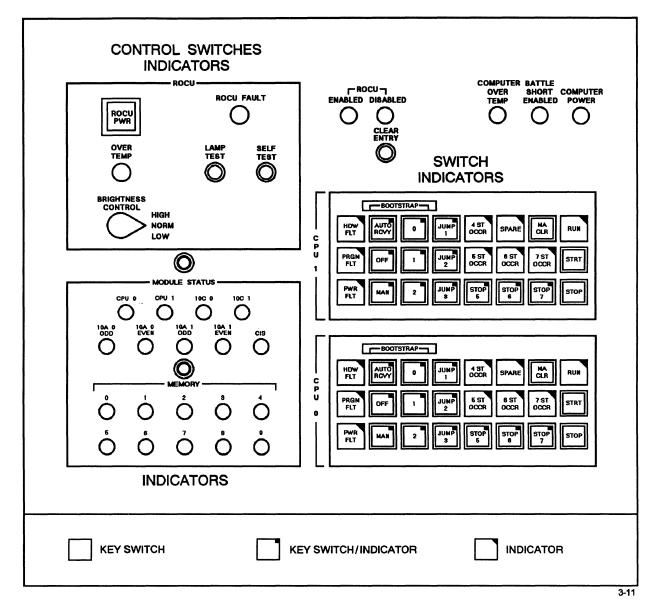

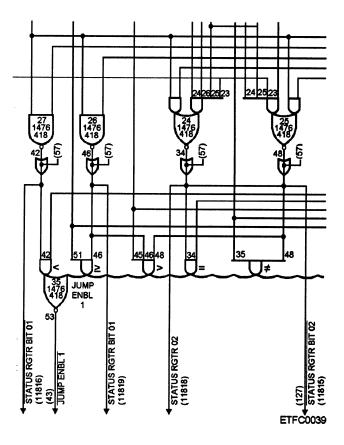

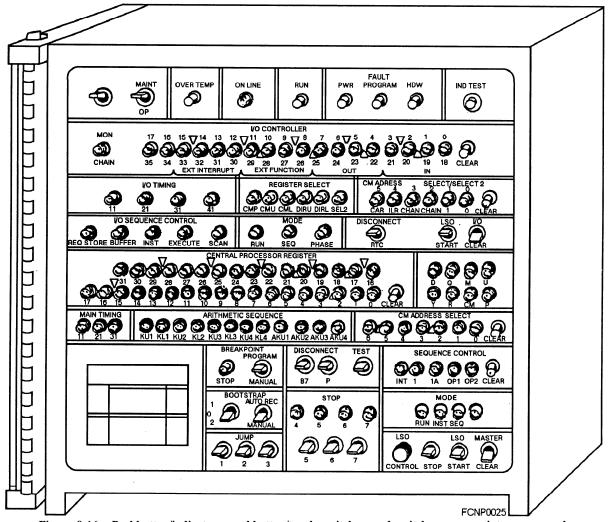

Figure 1-8 shows a portion of a maintenance panel/console of a mainframe computer. For example, notice the mode select push-button indicator, jump switches, and stop switches. You can use the jump switches and/or stop switches when performing

maintenance to set parameters for a diagnostic on the computer.

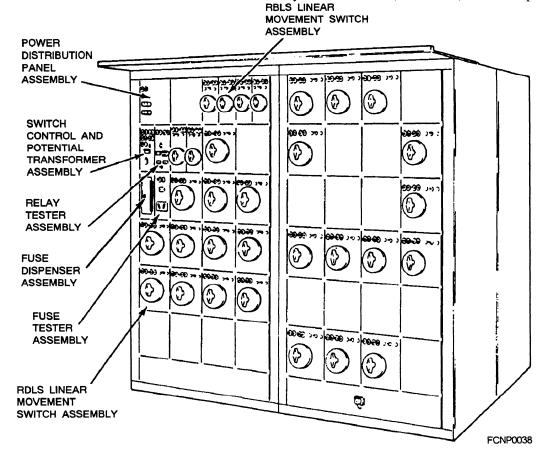

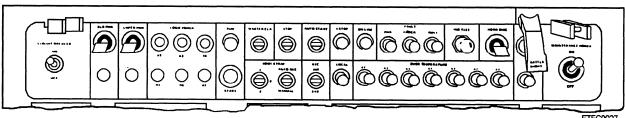

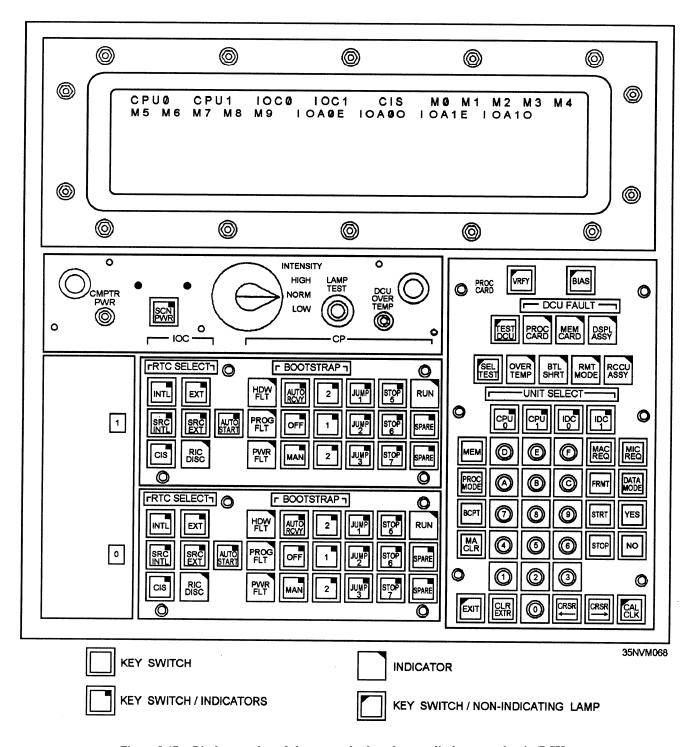

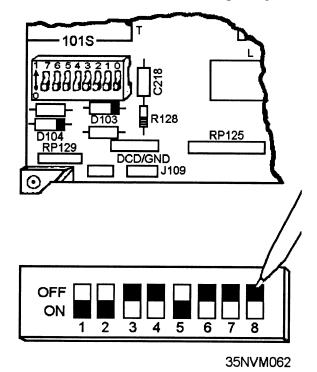

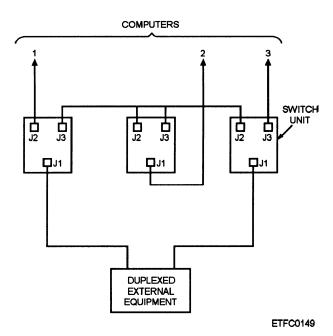

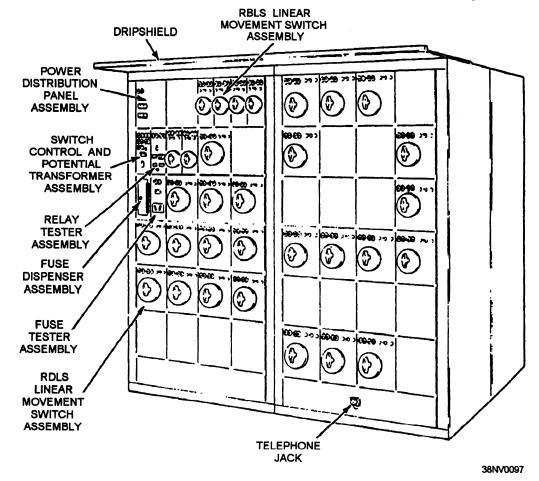

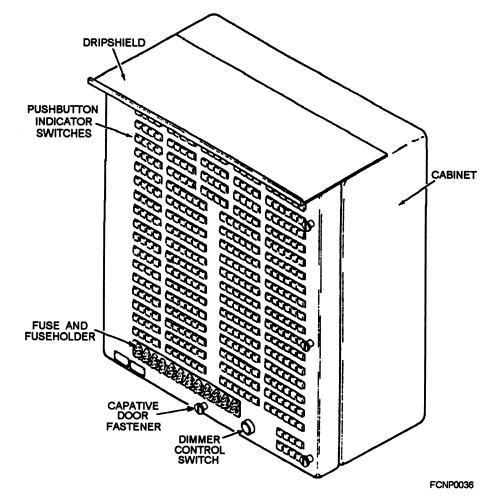

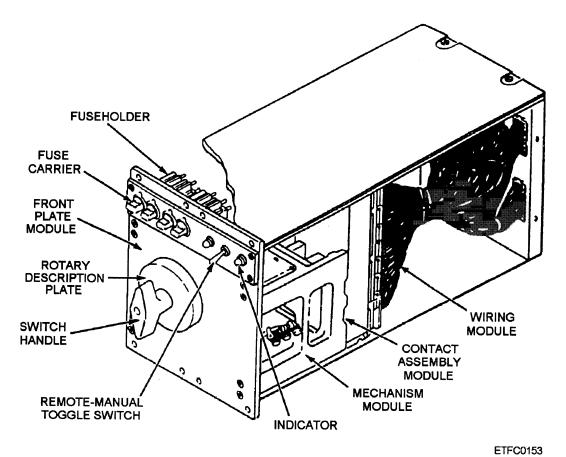

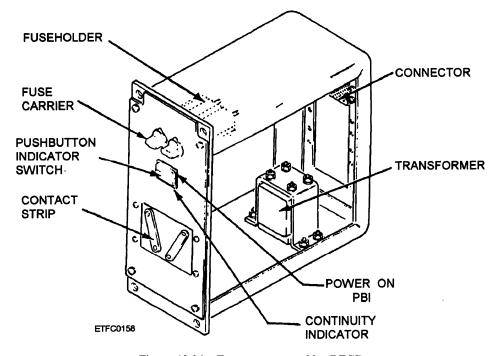

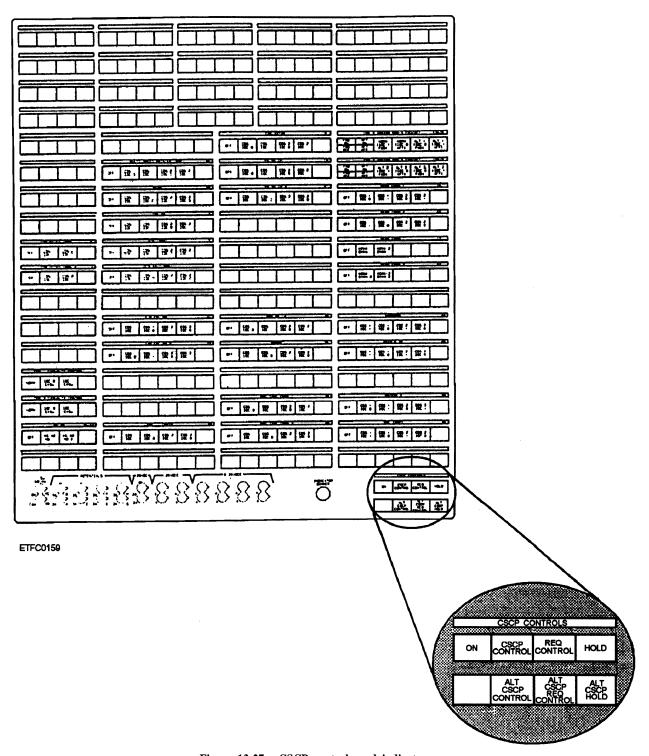

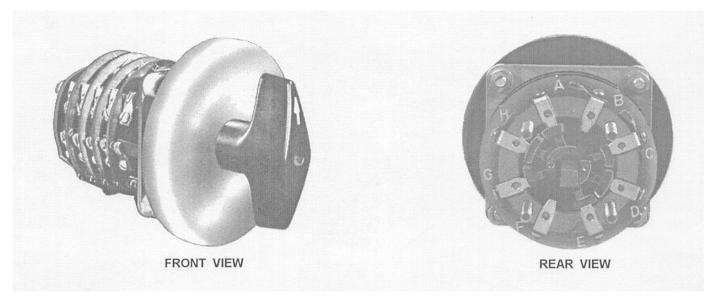

EXTERNAL CONTROLS. —Some computers use external controls to configure and set up the computer to enable it to communicate with peripherals and other systems. These controls work in conjunction with the software. Unless these controls are configured and set up properly, the computer cannot perform its functions correctly. The controls maybe set through digital switchboards or computer switching and control panels. Figure 1-9 is an illustration of a computer switching and control panel used on a CDS/NTDS system. Notice the push-button indicator switches available. You can use these to control the configuration and data routing.

#### Software

Once you have the hardware of the computer physically configured and set up correctly, the correct software must be installed and correctly configured/set up. When we speak about configuring and setting up the software, we are referring to specifying the resources the software is to use-what peripherals the system has, what communications, how much memory, what options you want set as defaults, and so on. In this way the hardware and software can talk to each other. The software and hardware have to work hand-in-hand with each other. Depending on the type of computer and type of system application, the hardware and software have the ability to control and/or are dependent on each other. Perform the following procedures when working with software:

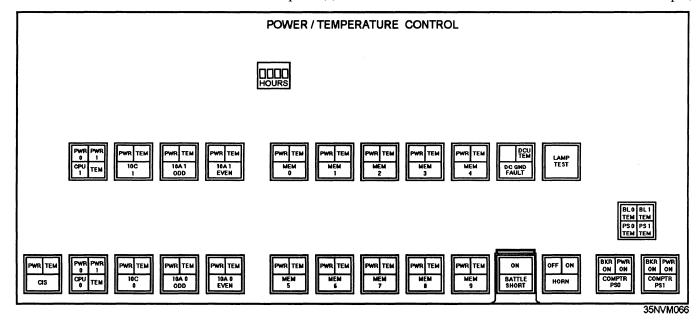

Figure 1-8.—A portion of a maintenance panel/console of a mainframe computer.

Figure 1-9.—Computer switching and control panel used on a CDS/NTDS system.

- Ensure you have the correct software for the type of system and type of computer

- Boot the computer

- Load the software via a peripheral device

- Initialize the system

- Monitor the computer for system operation and/or maintenance (tests—programmed and manual)

Your involvement with the software is directly dependent on the type of computer. Generally speaking, the bigger the computer system, the less involved you will be with configuring and setting up the software. All computer systems have an operating system to control their operations. An operating system is a collection of many programs the computer uses to manage its own resources and operations. These programs control the execution of other programs. The operating system used will depend on the type of computer and the systems platform. To communicate with the operating system of any computer, you need to

understand the operating system functions and the commands necessary to talk to it. This is also true of any applications software and utility programs you use. To communicate with any software, you need to know its functions and commands.

For mainframe computers used in tactical and tactical support applications, the software is designed by an outside support activity. With these systems you do not have to perform any initial configuration or setup of the software before using it. This has already been done by the activity that writes the operational program for the system's platform. The system operating commands you will use to talk to the computer to initialize and/or reconfigure the operational program are specific. Refer to your combat systems technical operations manuals (CSTOMs) or systems operations manuals (SOMs) for details.

For some minicomputer systems, such as the ones used for the SNAP I and II systems, the software has also already been configured and set up. You simply boot and initialize the system. System operating

commands for minicomputers are also specific. Refer to their system manuals and desktop guides for details.

The operational software a microcomputer uses can be off-the-shelf software or it can be software designed by an outside support activity to meet the specific requirements of a platform or system. Before a microcomputer may be used, you must configure and set up the software. When configuring and setting up the software for a microcomputer, there are several things you must be aware of. The operating system must be customized to the hardware of the computer system. This can be accomplished by following the step-by-step procedures in the users/owners manual. You will use operating system commands to setup the software to execute the program exactly as you have specified. For example, you could specify to the operating system program to automatically load a word processing program when the computer is turned on. You may want a beeper to alert you to a given situation such as when certain error conditions occur. You can set this. When using applications software with your operating system, you must ensure that the application software is compatible with the operating system. The application software will also use commands to execute its functions. Refer to operating systems and application software users manuals for details.

### ONLINE AND OFFLINE MODES OF OPERATION

Modes of operation are designed into the data systems and can be selected through hardware or software manipulation. Basically you can operate the computer either in an online or offline mode. What the computer can do in these modes depends on the type of computer and the software.

#### **Online**

When a computer is in the online mode of operation, it is performing operational functions. It is interfacing with other computers, peripherals, display systems, and communication systems to perform many tasks. And operationally, this means you must rely on the loaded software for the computer to perform its functions. The type of software the computer will use online will depend on the platform of the system (tactical, tactical support, and nontactical). A computer may perform the following types of operations in the online mode:

• Operational (includes application software)

• Maintenance (only when the computer's memory is large enough to accommodate the software can maintenance be performed while the operational program is still running)

#### **Offline**

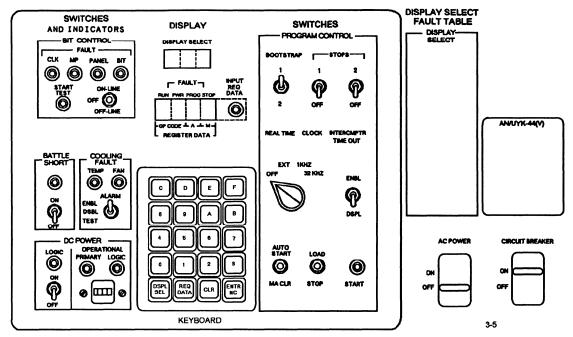

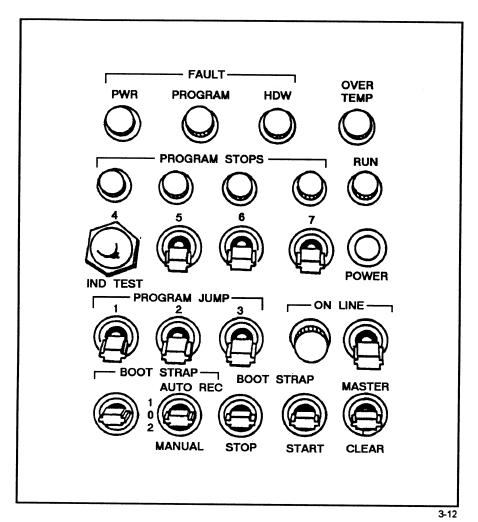

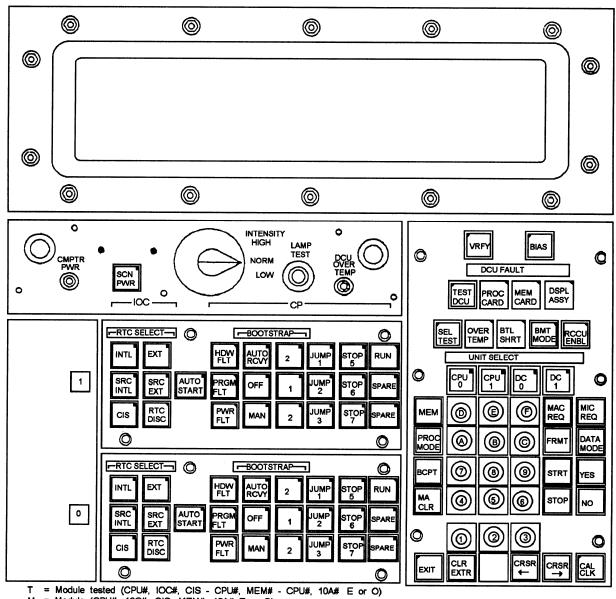

In the offline mode of operation, a computer is limited to performing maintenance. The computer can be either powered or unpowered depending on the maintenance you are performing. When you take the computer offline, you remove the computer from controlling a whole system. The computer is limited to interfacing with only a single system, such as a display system or a peripheral system, to perform controlled tests or a diagnostic to test itself. In this mode some computers have the capability to not only operate in the run mode but other detailed steps such as instruction mode and sequence mode. These modes are quite useful for troubleshooting malfunctions that can't be isolated using diagnostics or self-tests. Figure 1-10 shows the operating mode selections of a mainframe computer.

In the offline mode, you can perform the following types of maintenance:

- <u>Preventive maintenance</u> —Testing the computer using program controlled tests and internal tests such as diagnostics and self-checks; and cleaning filters, heat exchangers, and so on.

- <u>Corrective maintenance</u> —Troubleshooting the computer using program controlled tests and manual tests to isolate faults; and repairing faults by replacing bad parts or using solder and solderless techniques.

Figure 1-10.—The mode selections of a mainframe computer.

#### BATTLE SHORT MODE OF OPERATION

The battle short mode is used when it becomes necessary to run the computer continuously even though an overtemperature condition exists. The activation of a battle short switch will bypass overtemperature protection interlocks and power will be maintained to the computer for continued operation. An overtemperature condition is a result of a failed assembly or inadequate cooling. The requirement to run the computer continuously in an overtemperature condition usually only exists under battle conditions. Some computers are also equipped with a horn to warn an overtemperature condition exists.

### OPERATIONAL CAPABILITIES AND LIMITATIONS

It is important to know the capabilities and limitations of the hardware and software of any system you maintain. It is equally important to know whether the system can operate at reduced capability and still accomplish its mission. Some systems are designed with more than one computer (CPU), sufficient memory, and enough peripheral devices to enable them to function even when some devices are down. The

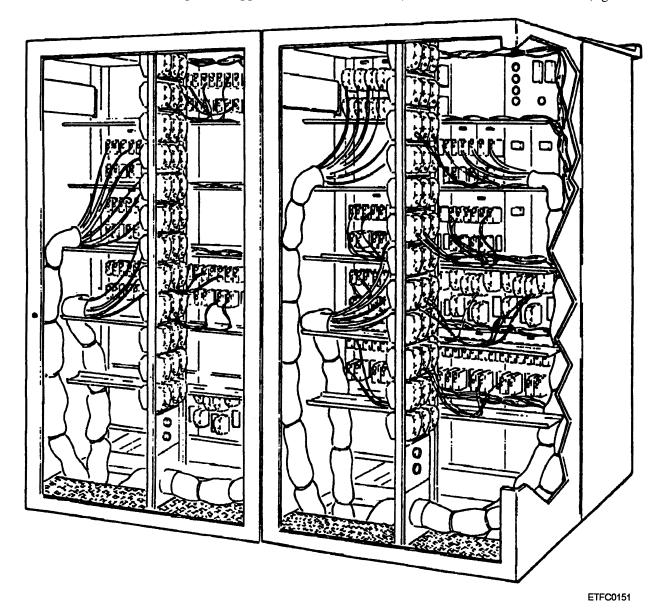

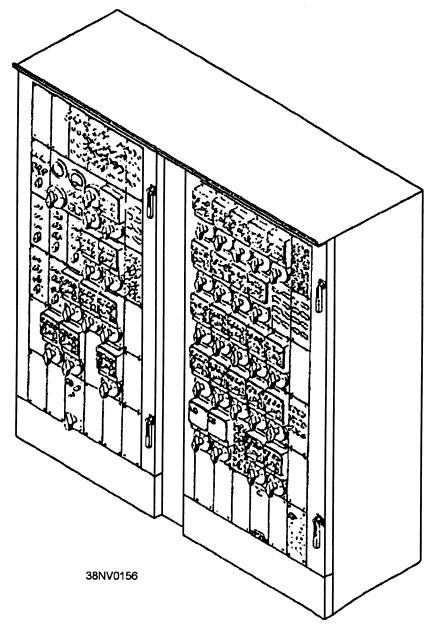

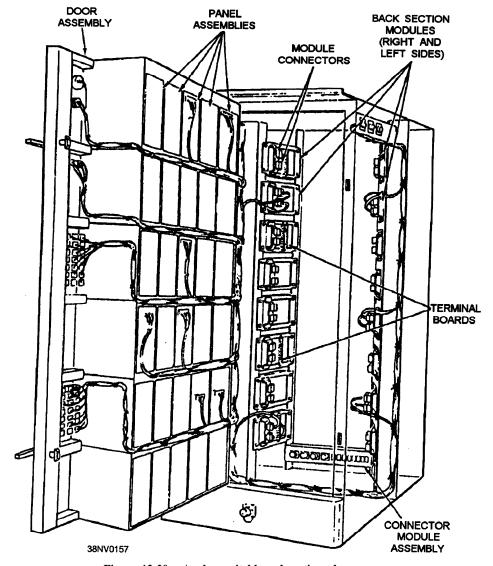

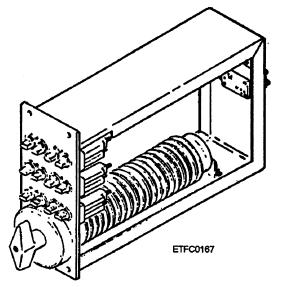

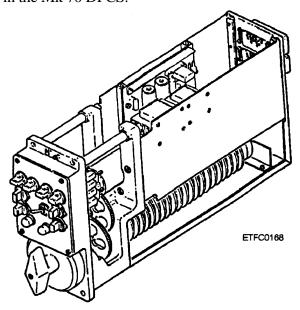

operational capabilities and limitations of a computer system can be controlled at the equipment through switchboards or control panels, or through commands to the software using an I/O device to talk to the computer. Figure 1-11 is an illustration of a digital fire control switchboard used on a CDS/NTDS to interconnect the computer to equipments and other major systems.

To find out the capabilities and limitations of a computer system, refer to your system operating manuals (SOMs) or combat systems technical operations manuals (CSTOMs) for details.

CDS/NTDS is an example of a system that uses a three-bay/one-bay computer configuration. This means it has four CPUs and can still meet its mission even if one of the CPUs is down. The term *reduced capabilities* means the computer system can perform its mission with fewer resources. Resources may be unavailable as a result of a casualty to a computer. If the memory of the computers allows it, you can take one of the computers offline to perform training. You can reduce the operational capability through the software using an I/O device to take the computer offline. This can be accomplished using operating system functions (commands). An example would be

Figure 1-11.—A digital fire control switchboard used on a CDS/NTDS.

a CDS/NTDS that normally uses a three-bay/one-bay computer configuration to operate at full capability. Because of a casualty to the one bay, that bay is dropped offline. The CDS/NTDS can still perform its basic mission, but the system is reduced because not all four computers are being used.

Devices that are used to bring the computer to reduced capability are switchboards and computer control panels. The operational program (software) must also be reconfigured to reflect the hardware reconfiguration. This can be accomplished at an I/O device using operating system functions (commands). Again refer to the SOMs or CSTOMs for exact details of your system's capabilities and limitations and the hardware and software required to reconfigure it.

### OPERATIONAL REQUIREMENTS OF COMPUTER SYSTEMS

Effective operation of computer systems also depends on security and on controlling electromagnetic disturbances. You'll need to pay particular attention to ADP security and electromagnetic interference (EMI). Lack of attention to these factors can seriously jeopardize the security and operation of a computer system.

#### **ADP Security**

The security of computers depends on administrative and physical controls. The administrative requirements (directives and instructions) will provide the policy and procedures to follow to meet the physical requirements. Let's highlight some of the things you will handle on a regular basis that require protection to ensure the security of the computer system.

- <u>Data and information</u> —For tactical and tactical support systems, the data the computer handles and makes available is classified. (Includes COMSEC material for tactical data links).

- <u>Passwords</u> —Used with nontactical systems (SNAP) to ensure only authorized users gain access to the computer system.

- Operational programs on magnetic tape, disk, and disk packs—For tactical and tactical support systems, these programs and any revisions (program patches) are classified. For nontactical systems, the operational programs may be copyrighted and require protection to avoid misuse.

- <u>Safe combinations</u> —For controlled spaces where computers are used.

- <u>Computers</u> —Computers must be safeguarded; they are an ADP asset.

Be sure you know where the emergency destruction procedures for the computer system are. They should be readily available. For more detailed information on guidelines that will aid in the security of computers, refer to OPNAVINST 5239.1, Department of the Navy Security Program for Automatic Data Processing Systems and OPNAVINST 5510.1, Department of the Navy Information and Personnel Security Program Regulation.

#### **Electromagnetic Interference**

Electromagnetic interference (EMI) is an electromagnetic or electrostatic disturbance that causes electronic equipment to malfunction or to produce undesirable responses or conditions that do not meet the requirements of interference tests. You must be more aware of the problems EMI causes and the solutions required to resolve these problems. No magic is involved in reducing or eliminating EMI. Everyday common sense approaches to maintaining equipment will resolve many problems caused by EMI.

**TYPES OF EMI.** —There are three types of EMI—natural, inherent, and manmade.

**Natural EMI.**—Natural interference is caused by natural events, such as snowstorms, electrical storms, rain particles, and solar radiation. It can cause problems with rf data links between shore, ship, and air, but few problems with modem digital data equipment.

**Inherent EMI.** —Inherent interference is noise within a piece of electronic equipment and is caused by thermal agitation or electrons flowing through circuit resistance.

Manmade EMI. —Manmade EMI is produced by a number of different classes of electrical and electronic equipment. The equipment includes, but is not limited to, transmitters, welders, power lines, motors and generators, lighting, engines and igniters, and electrical controllers. A number of these devices can cause severe EMI, which can degrade the operation of shipboard and shorebased computer systems.

EMI can be classified by its spectrum distribution. It can be either broadband or narrowband interference. These terms refer to the frequency spectrum the interference covers.

Narrowband EMI consists of a single frequency or a narrowband of interference frequencies. Narrowband EMI usually has a minor effect on communications or electronic equipment. It can be tuned out or filtered out.

Broadband EMI is not a discrete frequency. It occupies a relatively large part of the electromagnetic spectrum. It causes the majority of EMI problems in digital data equipment. It will be especially noticeable data on Link 11.

**CONTROL OF EMI.** —EMI can be controlled or eliminated if some simple procedures are followed and good installation practices adhered to. Let's look at control and reduction for shipboard and shorebased installations. Many of the problems are the same for both installations.

Shipboard EMI Control. —Shipboard EMI control is greatly simplified for the typical digital data installation. Because of the ship's steel hull and construction, a great deal of shielding and isolation are provided the typical shipboard computer room or digital equipment space. This blocks out the majority of broadband interference generated both internally and externally. Five major factors are considered in a shipboard computer and digital equipment installation. They are equipment location, equipment shielding, system and equipment grounds, interconnection cabling, and power source.

- <u>Equipment location</u> —Computers should be located in spaces that are free of sources of EMI. They should not be located in spaces that contain radars, radio transmitters, generators, or other rotating machinery.

- Equipment shielding —Digital computers should never be operated with drawers extended, cover plates removed, or doors open. Modem computers contain EMI-reducing gaskets and shields that enclose the equipment. Always reinstall cover plates with all the fasteners in place. If a cover plate or shield has to be removed in the course of corrective maintenance, ensure that the EMI reducing contacts or wire gaskets on the equipment opening are in good condition before the cover or shield is replaced.

- System and equipment grounds —System and equipment grounds are extremely important in digital computer installations. All cabinets should be grounded together on a common system ground bus. Each equipment cabinet is connected to the system ground by a heavy ground cable. The system ground is securely attached to the hull of the ship and provides a

good ground reference for the system. Paint on ground straps or on the metal decks where the ground straps are mechanically attached will result in poor electrical connections.

- Interconnecting cables —All interconnecting cables used in a shipboard digital data system should be shielded cables. They should be assembled correctly according to installation drawings. The shield and connector shell should be electrically connected and properly secured at either end. The cables should never be run in the same cableways as cables carrying rf signals or high- power pulse cables. The shielding protects the data cables from EMI to a great extent.

- <u>Power source</u> —Power lines for digital computers can provide a transmission path for EMI from machinery spaces. The majority of input power passes through noise elimination filters as it enters computers. Unusual random problems in digital computers can sometimes be traced to defective line filters.

**Shorebased EMI Control.** —Control of EMI at a shorebased installation requires the same consideration or the same factors as a shipboard system with two additions-site location and soil quality.

- <u>Site location</u> —Shorebased digital data equipment sites are sometimes built where the need dictates or where a convenient building is available. They are not always ideal sites. Sites built near a large industrial complex such as a shipyard repair facility (SRF) or a naval depot (NADEP) may be subjected to EMI. They also can cause power line fluctuations if the power source of the shore site and the SRF and NADEP are the same. Additional line filters and regulators for power lines may also be required to reduce EMI and provide line power within the limits prescribed by equipment manufacturers.

- <u>Soil quality</u> —At a shore installation, a system ground bus is usually attached to a grounding rod driven into the soil. If the soil is dry, sandy, rocky soil as found in the Southwestern United States and some places overseas, you will have a poor ground. A suspected system ground can be checked with an oscilloscope and 1:1 probe. Refer to *Electromagnetic Compatibility*, NAVELEX O967-LP-624-6010, for more information.

**DIRECTIVES.** —Many directives provide guidelines to follow for avoiding or reducing the effects of EMI. The EIMB handbook entitled *Electromagnetic Interference Reduction*, NAVSHIPS 0967-LP-000-0150, includes topics of shipboard EMI

tests and operating practices for EMI reduction. MIL-STD-1310 entitled *Shipboard Bonding, Grounding, and Other Techniques for Electromagnetic Compatibility and Safety,* is a military standard for the proper instruction of bonding straps and grounding cables. It is the reference for all shipboard electromagnetic capability (EMC) installations. It contains drawings that depict the proper shape of and lists materials required to construct bonding straps and grounding leads for shipboard electrical/electronics installation.

The Naval Shore Electronics Criteria handbook, *Electromagnetic Radiation Hazards*, NAVSEA OP 3565 Volumes 1 and 2, (parts 1 and 2) (NAVELEX 0967-LP-624-6010) has information on the reduction of EMI at shorebased facilities. All facets of grounding, shielding, and equipment bonding are contained in this highly informative handbook.

The Handbook of Shipboard Electromagnetic Shielding Practices, NAVSEA S9407-AB-HBK-010, provides specifications for cable spacing/shielding requirements and installation procedures that will minimize the effects of electromagnetic interference (EMI) on electronic equipment installed in naval vessels. It is intended for use by ship designers, planning engineers, personnel engaged in the installation of electronic equipment, overhaul and repair shipyards, tenders, and other repair and installation activities.

### SUMMARY—FUNDAMENTALS AND OPERATIONS OF COMPUTERS

This chapter has introduced you to computer functions, types of computers (mainframe computers, minicomputers, and microcomputers), operational uses, modes of operation, capabilities and limitations, and operational requirements. The following information summarizes important points you should have learned:

**COMPUTER FUNCTIONS** —Computers gather, process, store, disseminate, and display data. Data may be gathered manually or automatically or by a combination of both. Once processed, it can be stored either internally in memory banks or externally on disk or tape. Data maybe disseminated and stored, or it may be sent to a display device.

MAINFRAME COMPUTERS —Mainframe computers are large computers. Those used aboard Navy vessels are designed for ruggedness and are general-purpose, digital data computers with

multiprocessing capability. They usually have operator and remote consoles and a maintenance panel/display control unit (DCU). They have specific power and cooling requirements.

MINICOMPUTERS —Minicomputers are midrange computers. They are capable of stand-alone (self-contained) operation, or they maybe an embedded processor in a system or other type of digital device. They usually have a control and maintenance panel (CMP) or computer control panel. Like the mainframe, they have a rugged frame when used aboard ship, and they have specific power and cooling requirements.

MICROCOMPUTERS —Microcomputers (personal computers) are small, lightweight computers. Their central processing unit is contained on a single integrated chip (IC) and the entire computer system is contained on a handful of printed circuit boards in a small compact frame or cabinet.

**FUNCTIONAL OPERATION OF COM- PUTERS** —Computers exchange data with other computers, peripherals, and subsystems through a coordinated series of interrupts, requests, and acknowledges. The signal flow is coordinated by the operational program.

**INTERFACING** —Interfacing between the computer and other systems, subsystems, and equipment includes cabling and associated connectors. Methods of interfacing include both parallel and serial data transfers.

**OPERATIONAL USES** —Operational uses of computers include tactical and Naval Tactical Command Support Systems.

**COMPUTER SYSTEM CONFIGURA- TIONS** —Each system must be configured for operation and maintenance. The hardware and software must be compatible and must be set up to work together.

MODES OF OPERATION —Computer systems may be operated in online, offline, and battle short modes. Maintenance may be performed online if there is enough memory; otherwise it will be performed offline. Battle short mode is used when it is necessary to run the system continuously even though an overtemperature condition exists.

**OPERATIONAL SYSTEM REQUIRE- MENTS** —The operational capabilities and limitations can be controlled at the equipment, or through switchboards, control panels, or commands to the software. Effective operation depends on adherence to

ADP security requirements and reducing electromagnetic interference.

Study the block diagrams and technical manuals and learn all you can about how the computer operates.

You will also need to be able to operate the computer using maintenance and operator panels, display control units, and keyboards. You need to be familiar with operating the computer locally and remotely.

#### **CHAPTER 2**

# COMPUTER CONFIGURATIONS AND HARDWARE

#### INTRODUCTION

As a technician you must be able to recognize the different types of computers to maintain them. The functional units of any computer are consistent, no matter what type of computer you are maintaining. your main concern will be the architecture of the computers you maintain. Mainframe computers and minicomputers are usually housed in large- to medium-sized frames or cabinets suited for ruggedness. Microcomputers are housed in compact frames built more for their portability. If you can understand the architecture and general physical makeup, then you can maintain any type of computer. Technical manuals, owners' manuals, desktop guides, and system operating manuals are all excellent sources of information that you can use to learn the configuration of a specific computer system and its physical makeup.

#### After completing this chapter, you should be able to:

- Interpret the various types of diagrams and layouts used to specify unit configurations

- Describe the major hardware parts of a computer system

- Describe the unit connectors and cables of computer systems

- Describe the types of cooling systems used with computers

## TOPIC 1—COMPUTER CONFIGURATIONS/LAYOUTS

To be an effective technician, you must be familiar with the computer—inside and out. You must be able to understand the hardware as well as each of the functional units by using technical documents. The computer's technical manual will be your most reliable and effective source. Technical manuals usually start with a general description of the computer and become more detailed when discussing the hardware and each functiona.1 area of the computer. As a reminder, you must ensure you use the most current documentation when you perform maintenance on a computer. This is a **MUST**.

In our discussion of the computer in this topic, we examine the computer from two aspects—the

functional layout and the physical layout. Let's begin by examining how computers are functionally configured.

## FUNCTIONAL BLOCK DIAGRAMS OF COMPUTERS

A functional block diagram provides you with a general analysis of the principles of operation of the overall equipment, types of signals and their directional flow, and the major functional areas. Functional block diagrams can be of two types—the overall functional block diagram of the computer and the individual functional block diagrams of each functional unit. You can use both to gain a better understanding of the computer.

#### **Overall Functional Block Diagrams**

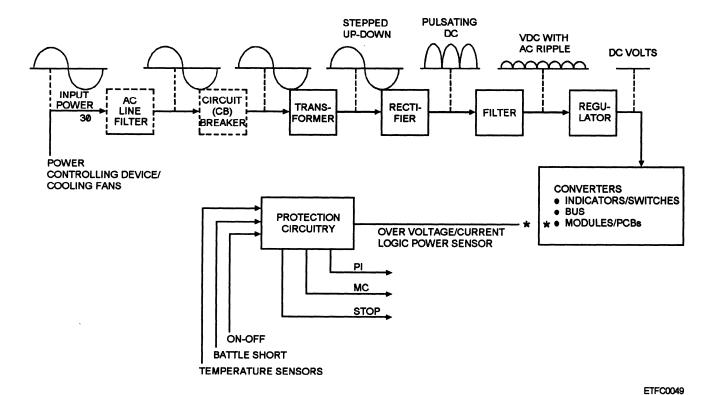

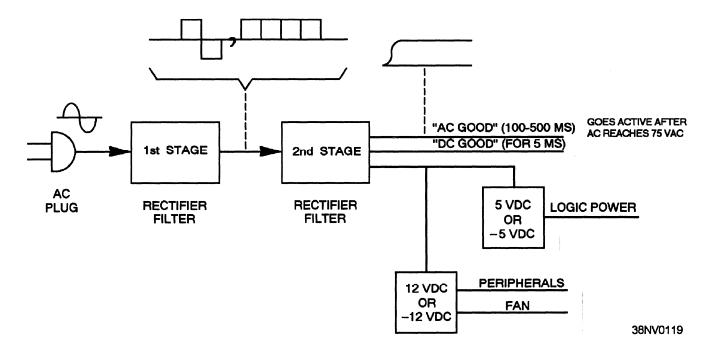

Overall functional block diagrams will show the functional areas of the computer and the supporting functions, such as power, cooling, and control of the computer. They will also show the types of signals exchanged between the functional areas and the supporting functions and the direction of signal flow. Figure 2-1 is an example of an overall functional block diagram of a computer.

Overall functional block diagrams are very useful when you perform corrective maintenance. After you have identified and elaborated on a problem, you can use the overall block diagram for the "listing of probable faulty functions." This will help you in your next step in the troubleshooting process—"localizing the faulty function." The overall functional block diagram can help you stay in the right area when troubleshooting.

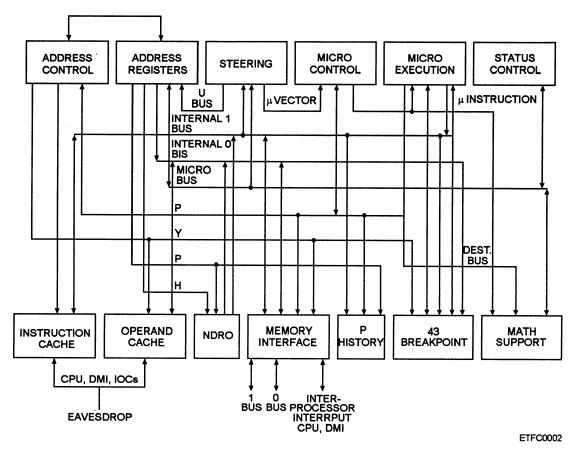

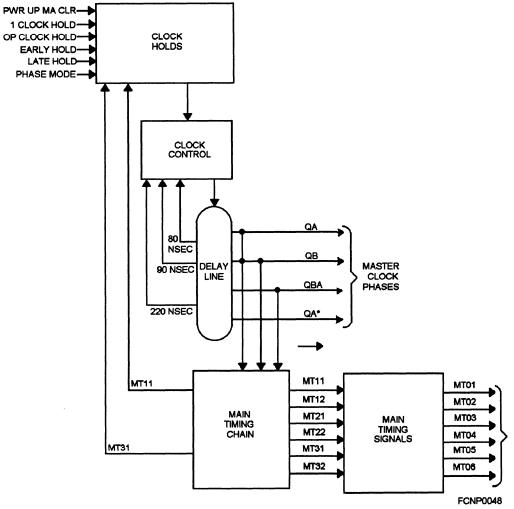

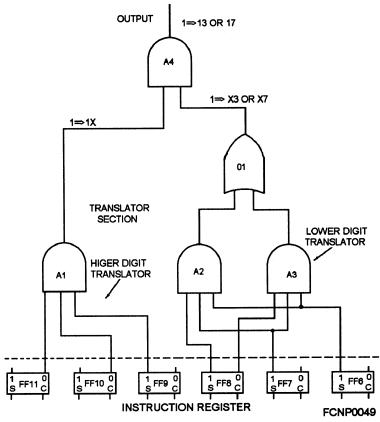

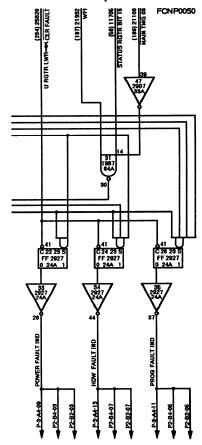

#### **Individual Functional Block Diagrams**

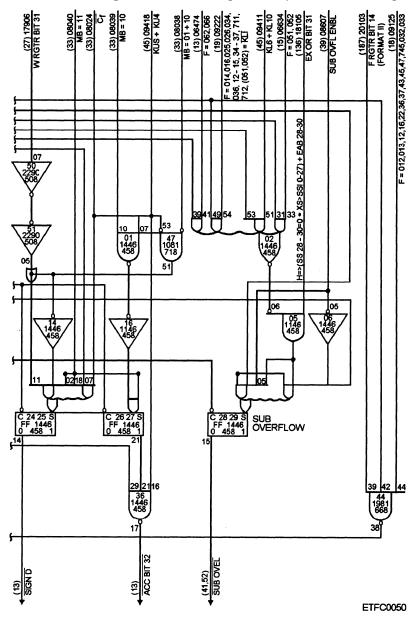

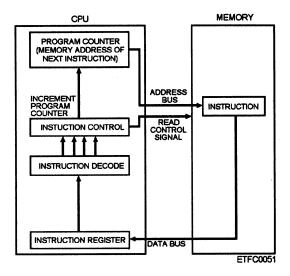

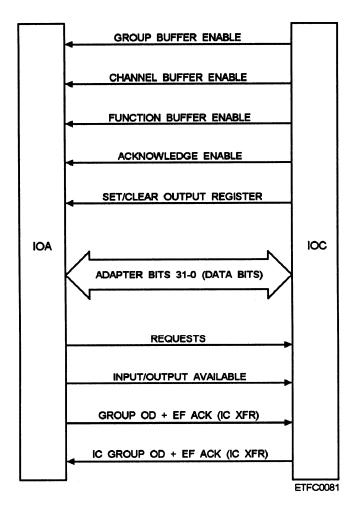

Once an overall description has been presented, the technical manual will give a general description of each functional area separately. These will include the major functional areas (CPU, I/O, and memory); the supporting functional areas (power supply and any special cooling requirements); and control of the computer (maintenance console/panel or display control unit and remote console/panel). When each functional area is described individually, an accompanying functional block diagram of that area will follow. Individual functional block diagrams can help you in your troubleshooting once you have "localized the faulty function." They provide a more detailed analysis of how that specific area of the computer operates. See figure 2-2 as an example of an individual functional block diagram of a CPU.

### FUNCTIONAL LAYOUTS OF COMPUTERS

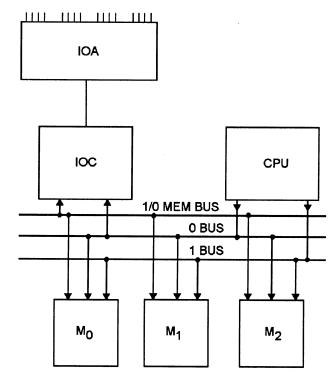

Functional layouts will show the major functional areas of the computer—CPU, I/O, and memory. Figure 2-3 is an example of an individual functional layout for a basic single cabinet configuration.

Systems that use a multiple configuration with more than one computer will also be depicted using an

Figure 2-1.—Example of an overall functional block diagram

Figure 2-2.—Example of an individual functional block diagram of a CPU.

NOTE: DATA ON BUS LINE IS BIDIRECTIONAL ARROWS

JUST INDICATE DIRECTION OF REQUEST

CONTROL SIGNAL

Figure 2-3.—Example of an individual functional layout of a single cabinet configuration.

ETFC0003

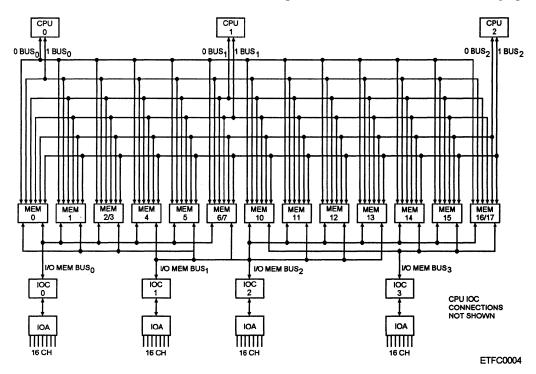

overall functional layout. Figure 2-4 is an example of a functional layout of a multiconfiguration computer system.

#### PHYSICAL LAYOUTS OF COMPUTERS

Physical layouts provide you with a "picture" of the computer. They are designed to show what the computer looks like and where each assembly, module, or console (maintenance and operator) of the computer is located. Physical layouts do **NOT** depict detailed descriptions of signal flow. Let's take a look at some of the ways computers are physically laid out.

#### **Overall Physical Layout of Computers**

Overall physical layouts will show you where each of the major parts of a single computer/computer set is located. The physical layouts and the terminology will vary with the type of computer and the manufacturer. The technical manual of each computer will provide you with the physical layout of that computer. Let's take a look at four types of physical layouts—modular, chassis or assembly, cage or rack, and motherboard or backplane.

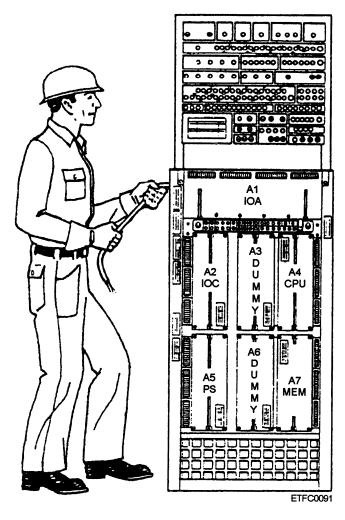

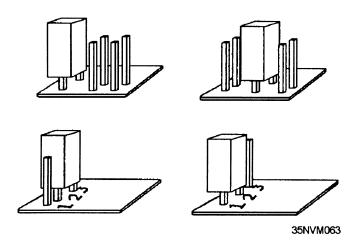

**MODULAR.** —The functional areas of the computer are modularized. In other words, the functional areas only contain the hardware for the function specified. For example, the module

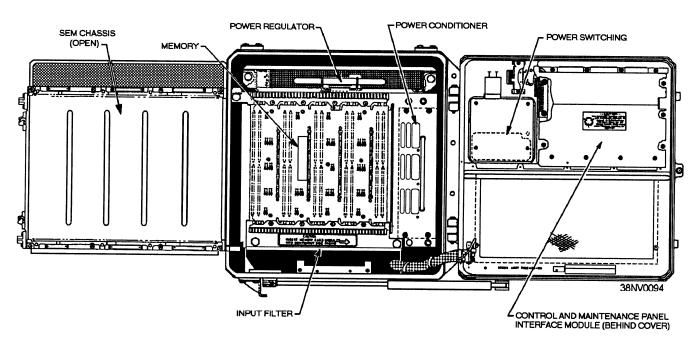

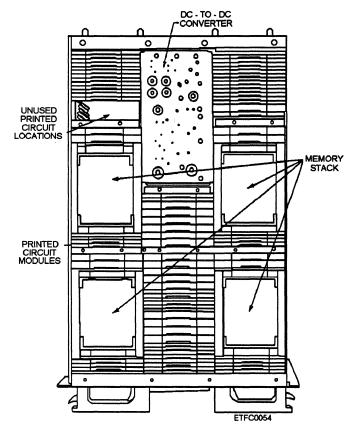

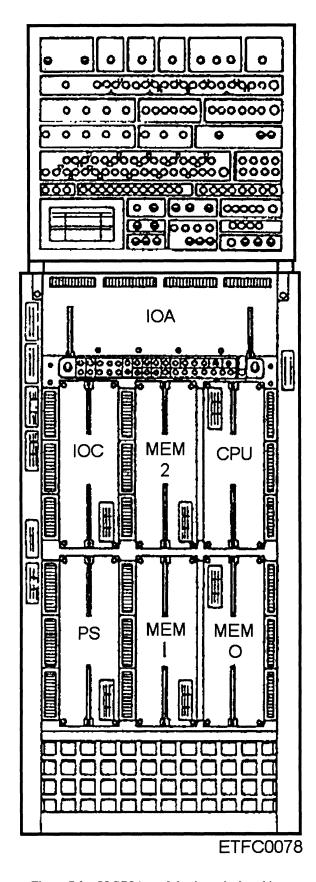

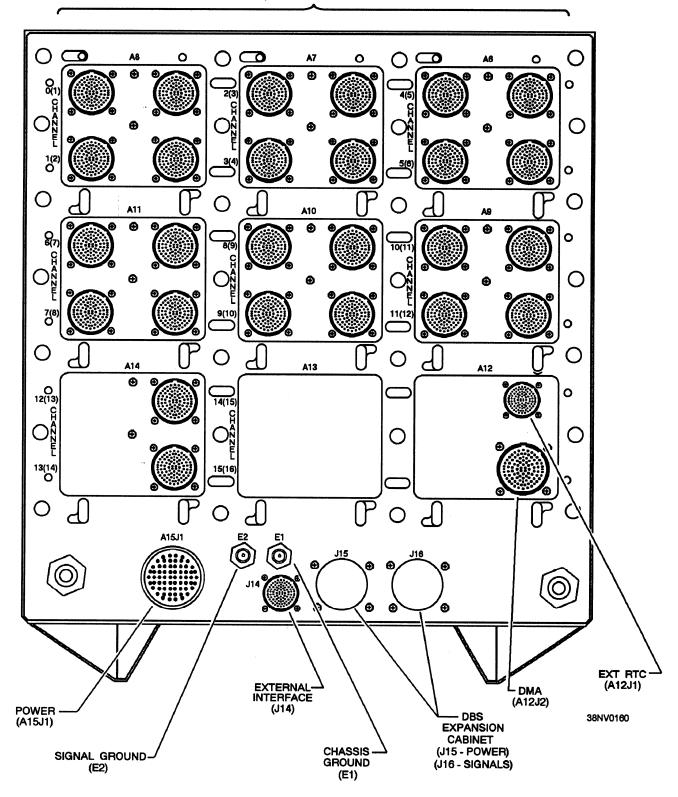

designated as the CPU only contains the subassemblies or printed circuit boards for the CPU functions. Figure 2-5 is an example that depicts the physical layout of a single mainframe computer set. Notice the modular layout. Also keep in mind that data systems that employ a multiple configuration will depict the minimum physical layout configuration.

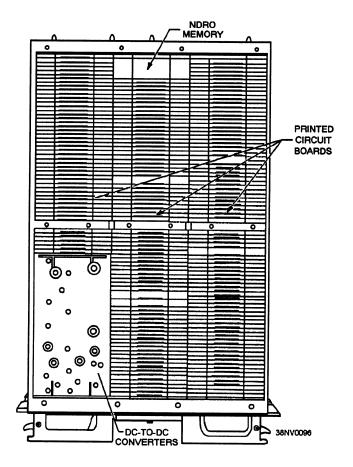

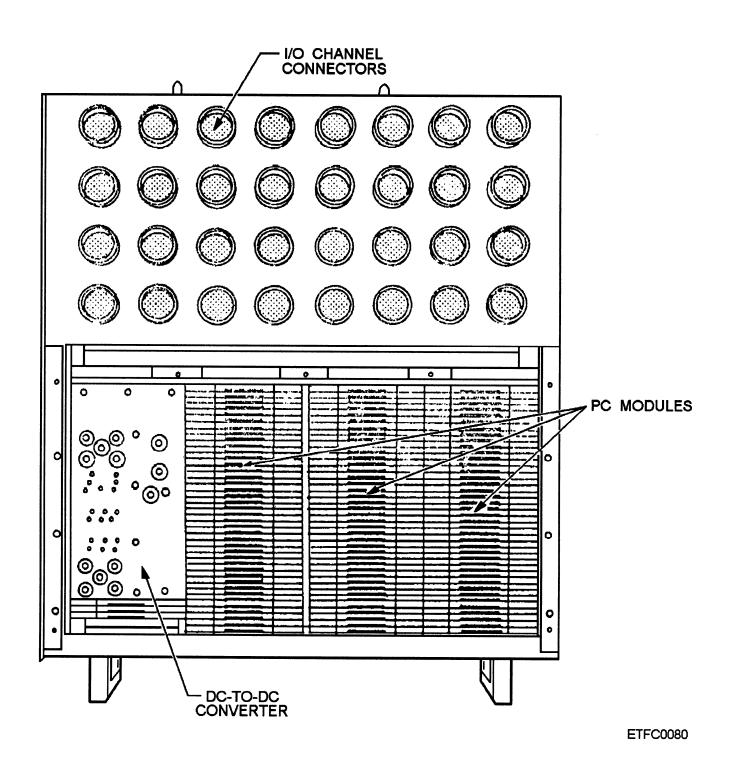

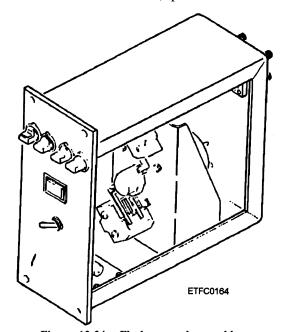

CHASSIS OR ASSEMBLY. —Chassis or assemblies usually are door mounted or slide mounted. Computers that use chassis or assemblies may contain one or more chassis or assemblies for the whole system. For example, one chassis may be dedicated only for memory, one for the power supply, and a third chassis or assembly for the rest of the computer (the CPU and the I/O). One to several subassemblies or printed circuit boards (pcb's) may comprise the CPU, I/O, or memory. Figure 2-6 is an illustration of a chassis used in a minicomputer.

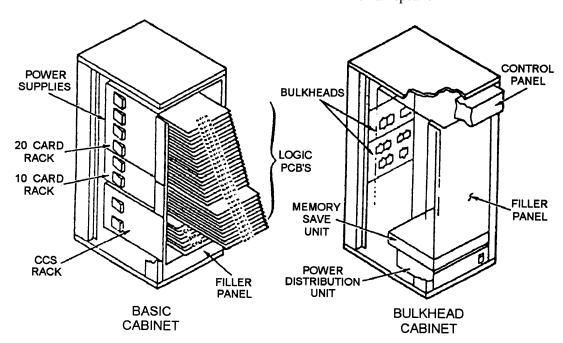

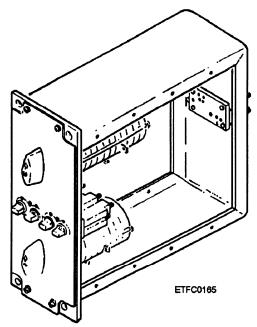

CARD CAGE OR RACK. —A card-cage or rack-designed computer will generally contain the major functional areas of a computer. The card cage or rack is usually centrally mounted in the overall computer chassis. The number of subassemblies or pcb's contained in a card cage or rack can vary from just a few to many depending on the technology of the computer. One or more pcb's may comprise a functional area. A card cage or rack is fixed in a single position; it does not slide out or swing open like a door.

Figure 2-4.—Example of a functional layout of a multiconfiguration computer system.

Figure 2-5.—Physica1 layout of a single mainframe computer set.

Figure 2-6.—Example of a chassis used in a minicomputer.

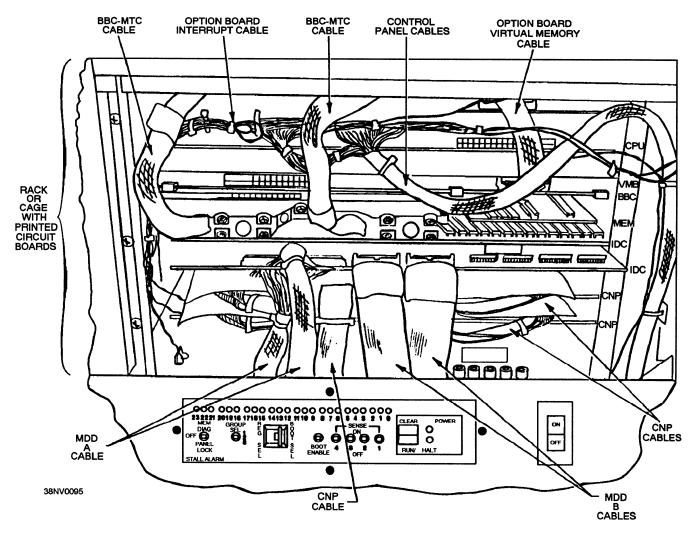

Figure 2-7.—Physical layout of a card cage or rack used in a minicomputer.

Figure 2-7 is an example of a card cage or rack used in a minicomputer.

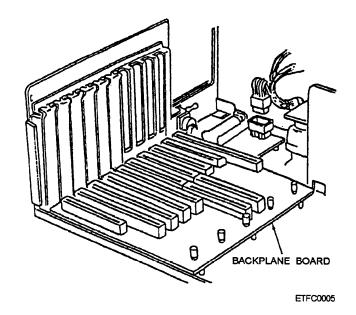

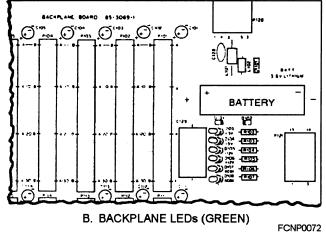

#### BACKPLANE OR MOTHERBOARD.—

Backplanes or motherboards are stationary and are generally located inside the computer's chassis. In this arrangement, all the subassemblies or pcb's needed to run the computer are contained on a single backplane or motherboard. The number of functional areas contained on a single subassembly or pcb may vary according to the technology of the computer. Computers that use a backplane or motherboard are compact. Figure 2-8 is an example of a backplane used in a microcomputer.

# **Individual Physical Layouts of Computer Parts**

Using individual physical layouts, the technical manuals depict each part of the computer separately. By separating each major part of the computer, you can break down the computer from a whole unit to the

Figure 2-8.—Example of a backplane used in a microcomputer.

frame/cabinet to see how subassemblies or printed circuit boards are laid out in each assembly, chassis, or module. Check your computer's technical manual for specific details.

Examples of the parts of a computer that are depicted in individual physical layouts are the following:

- Maintenance and operator console/panel location and its identification of individual computer controls

- Display control unit location and identification of its individual controls

- Remote console/panel location and identification of its individual computer controls

- Mainframe or cabinet and its contents

- Assemblies or chassis and their contents

- Subassembly or printed circuit card locations and their component locations

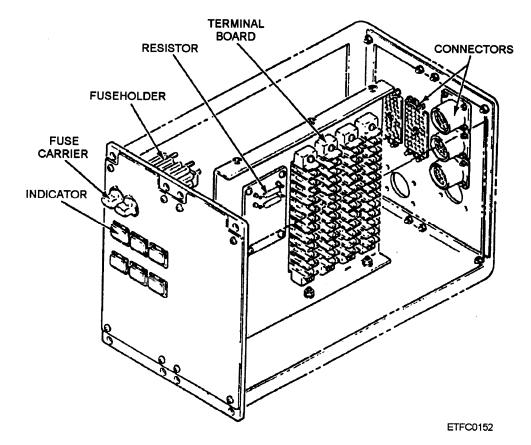

Figure 2-9 is an example of an individual physical layout of a module used in a mainframe computer. Notice how the contents of the module are physically laid out.

For some computer units/parts, individual physical layouts are not provided in the technical manual. For example, a layout would not be provided for a power supply in a microcomputer that is sealed. You only need to determine that the power supply has a faulty output and turn the power supply in for a replacement. If you never have a reason or are never required to open a unit/part to repair it, there is no need to have an individual physical layout.

We have discussed unit configurations, now let's focus our attention on the hardware of a computer. We start with the frame/cabinet, some of the parts that are contained in a frame/cabinet, computer connectors, cables, and fmally computer cooling hardware.

#### **TOPIC 2—COMPUTER HARDWARE**

The hardware makeup of each computer will vary. Generally speaking, the type of computer and platform of the data system will dictate the physical makeup of the computer. Large computers tend to be more rugged and the modules or assemblies more tightly assembled than a microcomputer (PC), which is generally more adapted for portability and not for ruggedness. Let's take a look at some of the hardware used in computers.

Figure 2-9.—Example of an individual physical layout of a module used in a mainframe computer.

We'll start with the frame or cabinet and work our way down to the pcb's, subassemblies, and the support hardware.

#### **COMPUTER FRAMES/CABINETS**

The frame or cabinet (often called the chassis) houses the computer. It holds or supports all the parts (the functional areas) of the computer. As you will see there are different designs based on the different types of computers and the types of systems on which they are used. These dictate the type of arrangement the frame or cabinet has. Inmost cases, the frame or cabinet also contains the support areas-the power supply module or unit and hardware for cooling.

The frame or cabinet can provide limited protection for the computer against such hazards as shock, moisture, and EMI or RFI. As a general rule of thumb, except for PCs, all computers aboard ship are shock mounted to withstand the constant motion of the ship as well as sudden impact. For computers that are used ashore, the frame or cabinet is secured to the floor. The

size of the frame or cabinet of a computer is a general indication of the type of computer and the type of data system the computer is used on. Consult your computer's technical manual or owner's manual for parts, tools, and test equipment needed in the maintenance of the computer.

Let's take a look at the designs or types of frames/cabinets—modular, chassis or assembly, cage or rack, and motherboard or backplane. Some computers use combinations of these designs.

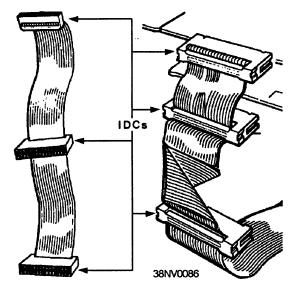

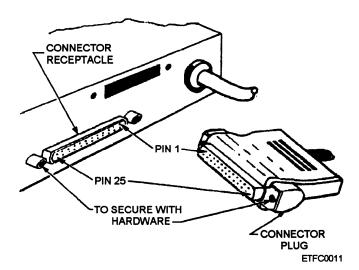

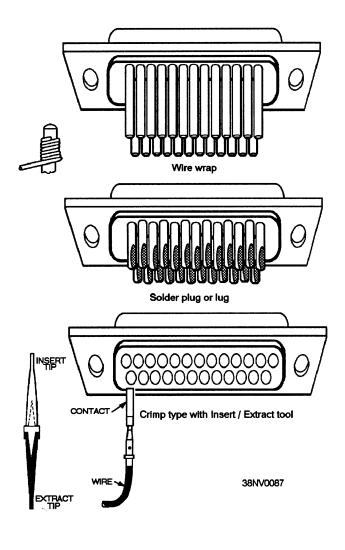

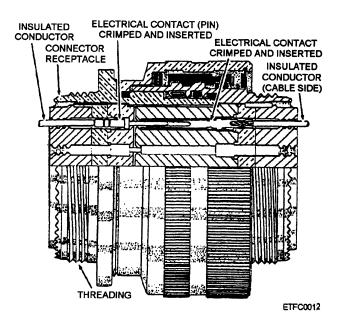

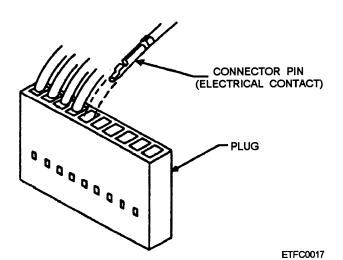

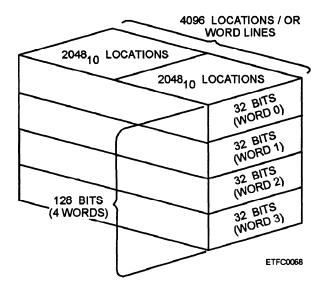

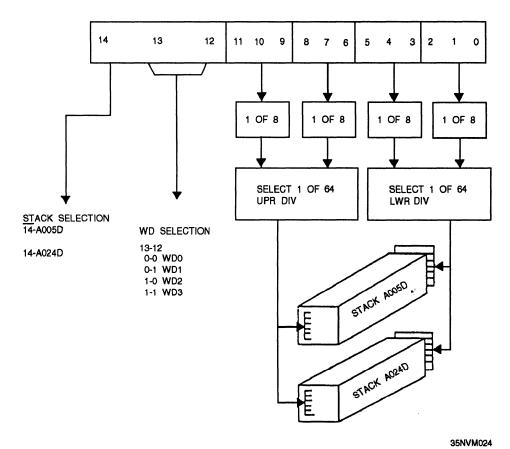

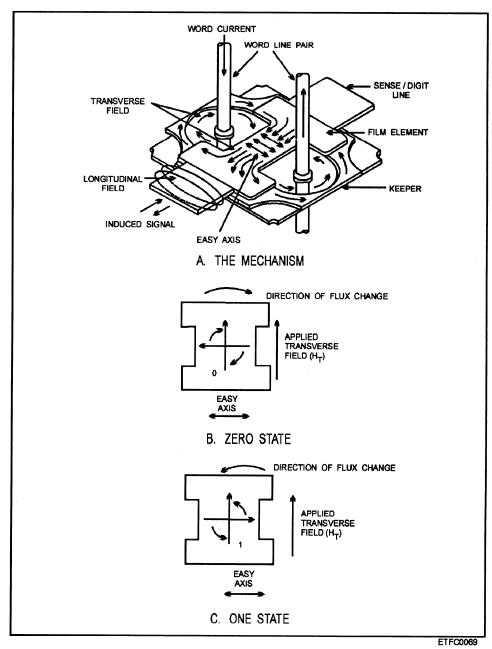

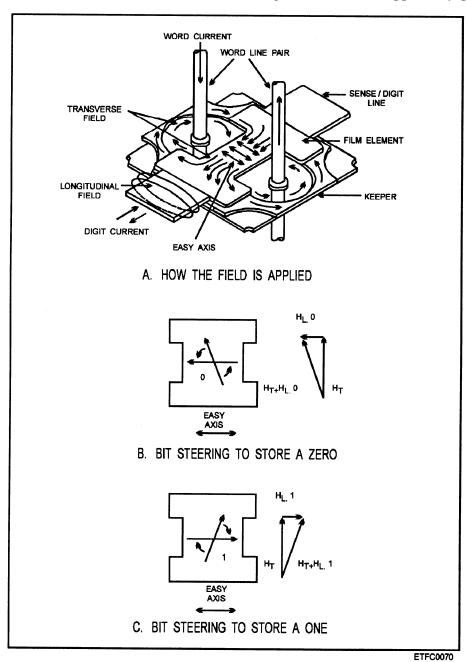

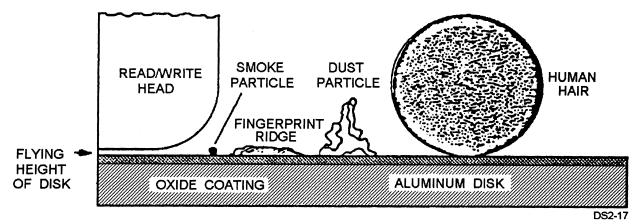

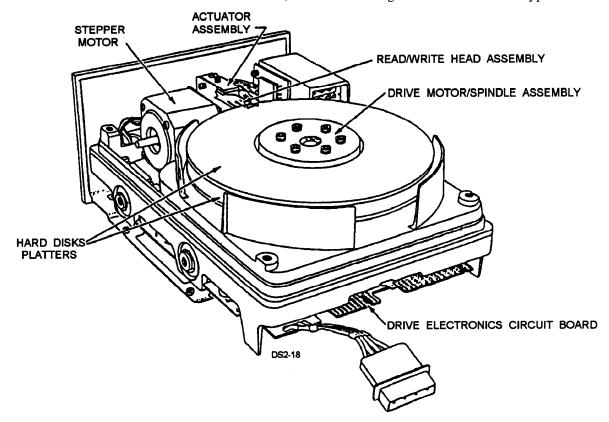

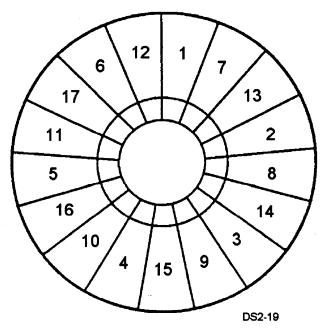

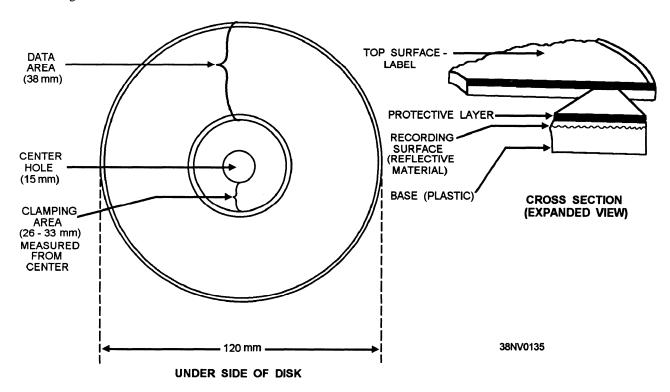

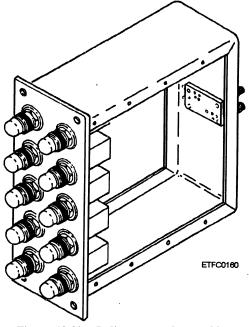

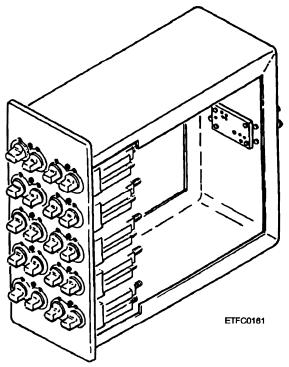

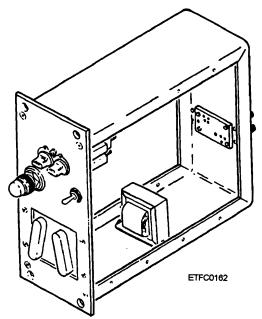

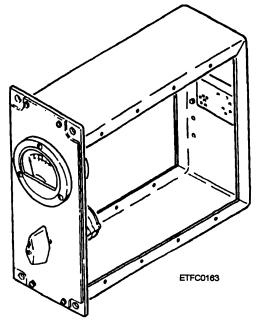

#### **Modular-Designed Computer Frames/Cabinets**